ADM-VPX3-9Z2 User Manual

V1.1 - 16th January 2020

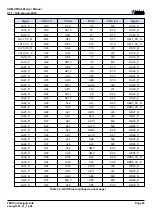

3.7.5 USB Interfaces

The 9Z2 has three external USB interfaces.

Interfaces USB1 and USB2 are connected between VPX P1 connector and the PS side of the MPSoC.

The PS acts as the USB host to interfaces USB1 and USB2.

USB3 is a direct connection between microUSB connector J3 and the Platform Manager / System Monitor

Microcontroller.

PS

PHY

USB3

4 port

Hub

VPX

P1

USB1

USB2

Micro

USB

Platform

Manager

Figure 8 : USB Interfaces

3.8 Zynq PL Block

3.8.1 I/O Bank Voltages

The FPGA IO is arranged in banks, each with their own supply pins. The bank numbers, their voltage and

IO Banks

Voltage

Purpose

65, 66, 67

FMC_VADJ

FMC+ GPIO - LA and HA

64

FMC_VIO_B

FMC+ GPIO - HB

25, 46, 47

FMC3_VADJ

FMC+ GPIO

47, 48

2.5V

VPX P2 GPIO

50

3.3V

Optical Module Setup and Control

49

1.8V

Unused

Table 20 : PL FPGA IO Banks

3.8.2 PL MGT Links

There are a total of 32 Multi-Gigabit Transceiver (MGT) links connected to the FPGA:

Links

Banks

Width

Max Rate Connection

DP(15:0)

228, 229,

230, 128

16

24Gbps

Direct links to FMC+ Socket (J1)

DP(19:16) 129

4

12Gbps

Links muxed to EITHER FMC+ Socket (J1) OR VPX P2 Optical

Module

DP(23:20) 130

4

12Gbps

Links muxed to EITHER FMC+ Socket (J1) OR VPX P1 Connector

Table 21 : PL MGT Links

Note: Links that are multiplexed are restricted to a maximum bitrate of 12Gbps.

Page 16

Functional Description

ad-ug-1323_v1_1.pdf