ADM-VPX3-9Z2 User Manual

V1.1 - 16th January 2020

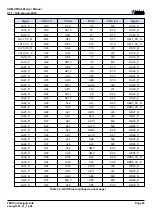

Signal

FMC (J1)

FPGA

|

FPGA

FMC (J1)

Signal

LA15_P

H19

AC2

|

V6

F16

HA15_P

LA16_N

G19

AA10

|

T6

E16

HA16_N

LA16_P

G18

AA11

|

T7

E15

HA16_P

LA17_CC_N

D21

AF5

|

P9

K17

HA17_CC_N

LA17_CC_P

D20

AE5

|

P10

K16

HA17_CC_P

LA18_CC_N

C23

AG4

|

T10

J19

HA18_N

LA18_CC_P

C22

AG5

|

U10

J18

HA18_P

LA19_N

H23

AE9

|

V7

F20

HA19_N

LA19_P

H22

AD10

|

V8

F19

HA19_P

LA20_N

G22

AF12

|

U8

E19

HA20_N

LA20_P

G21

AE12

|

U9

E18

HA20_P

LA21_N

H26

AH3

|

AC9

K20

HA21_N

LA21_P

H25

AG3

|

AB9

K19

HA21_P

LA22_N

G25

AG11

|

AA12

J22

HA22_N

LA22_P

G24

AF11

|

Y12

J21

HA22_P

LA23_N

D24

AH11

|

Y9

K23

HA23_N

LA23_P

D23

AH12

|

Y10

K22

HA23_P

LA24_N

H29

AJ2

|

AL7

K26

HB00_CC_N

LA24_P

H28

AH2

|

AL8

K25

HB00_CC_P

LA25_N

G28

AJ1

|

AM11

J25

HB01_N

LA25_P

G27

AH1

|

AL11

J24

HB01_P

LA26_N

D27

AF1

|

AK10

F23

HB02_N

LA26_P

D26

AF2

|

AJ10

F22

HB02_P

LA27_N

C27

AF3

|

AM10

E22

HB03_N

LA27_P

C26

AE3

|

AL10

E21

HB03_P

LA28_N

H32

AJ5

|

AK9

F26

HB04_N

LA28_P

H31

AJ6

|

AJ9

F25

HB04_P

LA29_N

G31

AJ4

|

AM8

E25

HB05_N

LA29_P

G30

AH4

|

AM9

E24

HB05_P

LA30_N

H35

AH8

|

AL5

K29

HB06_CC_N

LA30_P

H34

AG8

|

AL6

K28

HB06_CC_P

LA31_N

G34

AH6

|

AP10

J28

HB07_N

LA31_P

G33

AH7

|

AP11

J27

HB07_P

LA32_N

H38

AG9

|

AK4

F29

HB08_N

LA32_P

H37

AG10

|

AK5

F28

HB08_P

LA33_N

G37

AF8

|

AP4

E28

HB09_N

Table 32 : GPIO Pins (continued on next page)

Page 25

FMC Pin Assignments

ad-ug-1323_v1_1.pdf