SERIES IP503 INDUSTRIAL I/O PACK EIA/TIA-232E & CENTRONICS COMMUNICATION MODULE

___________________________________________________________________________________________

- 5 -

P2 Pin Signal Descriptions continued

SIGNAL

DESCRIPTION

RTS_A*

RTS_B*

Request-to-Send Output - The RTS output is

turned on to tell the modem it is ready to send

data. This signal has no effect on the transmit or

receive operation. This signal can be set low

(active) by writing a 1 to the Modem Control

Register

DTR_A*

DTR_B*

Data Terminal Ready Output - used to signal a

modem or data set to indicate equipment readiness

to establish communications. Placed in the active

state by setting bit 0 of the Modem Control Register

The DTR output is placed in the inactive (high)

state either as a result of a system reset during

loop mode operation, or by resetting bit 0 (DTR*) of

the Modem Control Register

CTS_A*

CTS_B*

Clear-to-Send Input - Turned on by the receiving

device to indicate it is ready to receive data. The

input status of this signal can be read via bit 4 of

the Modem Status Register. CTS has no effect on

the transmit or receive operation

RI_A*

RI_B*

Ring Detect Indicator Input - When the receiving

device receives a call (auto-answer), RI is switched

on and off in sequence with the phone ringer to

signal that a call is present and a remote modem is

requesting a dial-up connection. The status of this

signal can be read via bit 6 of the Modem Status

Register

Refer to Drawing 4501-569 for a detailed explanation of the

EIA/TIA-232E interface levels. See Drawing 4501-572 for null-

modem connections

Noise and Grounding Considerations

The serial and parallel channels of this module are non-

isolated and share a common signal ground connection. Further,

the IP503 is non-isolated between the logic and field I/O grounds

since signal common is electrically connected to the IP module

ground. Consequently, the field interface connections are not

isolated from the carrier board and backplane. Care should be

taken in designing installations without isolation to avoid noise

pickup and ground loops caused by multiple ground connections

The signal ground connection at the communication ports are

common to the IP interface ground, which is typically common to

safety (chassis) ground when mounted on a carrier board and

inserted in a backplane. As such, be careful not to attach signal

ground to safety ground via any device connected to these ports,

or a ground loop will be produced, and this may adversely affect

operation

The communication cabling of the P2 interface carries digital

data at a high transfer rate. For best performance, increased

signal integrity, and safety reasons, you should isolate these

connections away from power and other wiring to avoid noise-

coupling and crosstalk interference. Historically, RS-232

communication distances were generally limited to less than 50

feet. Actual distance limits are set by the EIA/TIA-232E driver

load capacitance limit (2500pF)In any case, interface cabling and

ground wiring should always be kept as short as possible for best

performance. Please refer to Drawing 4501-550 for example

connections and proper grounding practices

IP Logic Interface Connector (P1)

P1 of the IP module provides the logic interface to the mating

connector on the carrier board. This connector is a 50-pin female

receptacle header (AMP 173279-3 or equivalent) which mates to

the male connector of the carrier board (AMP 173280-3 or

equivalent)This provides excellent connection integrity and

utilizes gold-plating in the mating area. Threaded metric M2

screws and spacers are supplied with the IP module to provide

additional stability for harsh environments (see Drawing 4501-434

for assembly details)Field and logic side connectors are keyed to

avoid incorrect assembly. The pin assignments of P1 are

standard for all IP modules according to the Industrial I/O Pack

Specification (see Table 22)

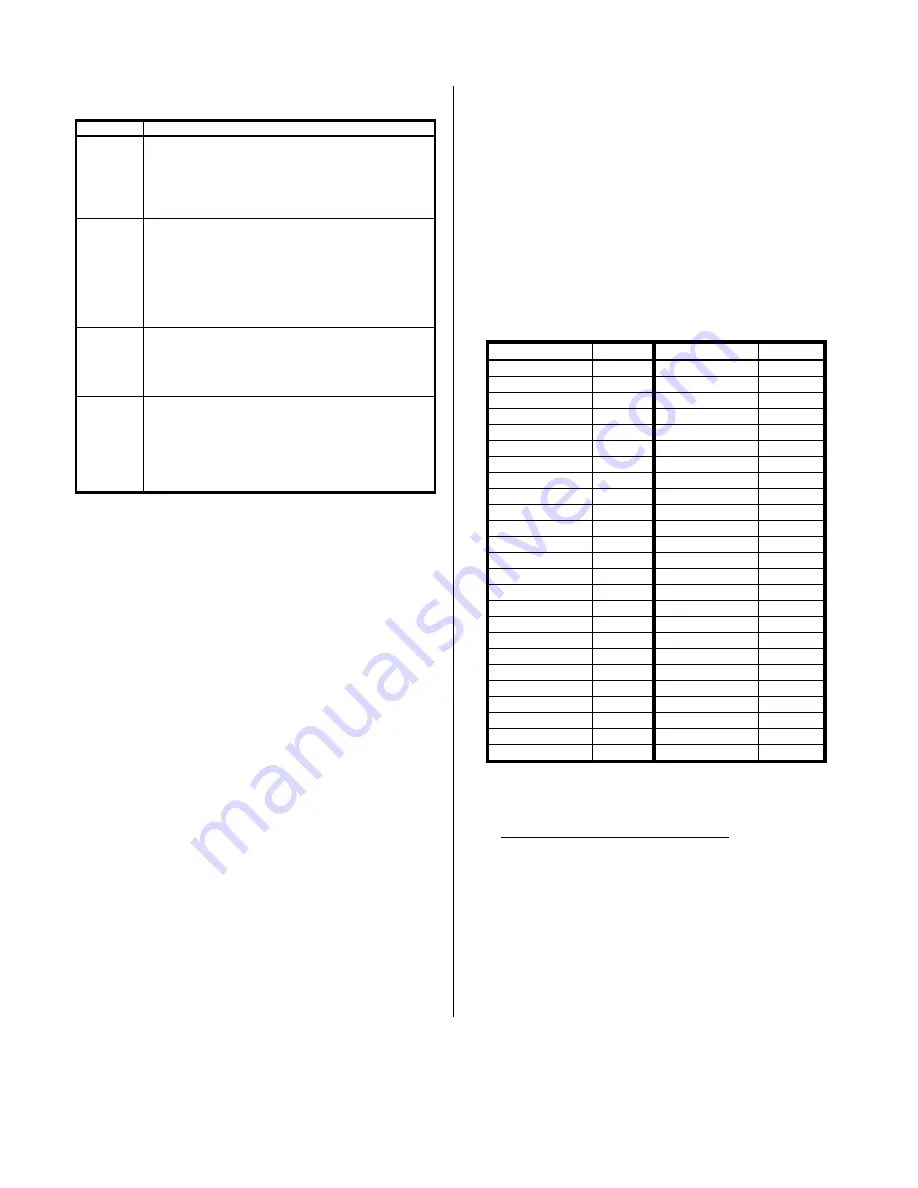

Table 22:Standard Logic Interface Connections (P1)

Pin Description

Number

Pin Description

Number

GND

1

GND

26

CLK

2

+5V

27

Reset*

3

R/W*

28

D00

4

IDSEL*

29

D01

5

DMAReq0*

30

D02

6

MEMSEL*

31

D03

7

DMAReq1*

32

D04

8

IntSel*

33

D05

9

DMAck0*

34

D06

10

IOSEL*

35

D07

11

RESERVED

36

D08

12

A1

37

D09

13

DMAEnd*

38

D10

14

A2

39

D11

15

ERROR*

40

D12

16

A3

41

D13

17

INTReq0*

42

D14

18

A4

43

D15

19

INTReq1*

44

BS0*

20

A5

45

BS1*

21

STROBE*

46

-12V

22

A6

47

+12V

23

ACK*

48

+5V

24

RESERVED

49

GND

25

GND

50

An Asterisk (*) is used to indicate an active-low signal

BOLD ITALIC Logic Lines are NOT USED by this IP Model

30 PROGRAMMING INFORMATION

ADDRESS MAPS

This board is addressable in the Industrial Pack I/O space to

control the interface configuration, data transfer, and status

monitoring of two EIA/TIA-232E serial ports and one Centronics

parallel port. As such, three types of information are stored in the

I/O space: control, status, and data. These registers are listed

below along with their mnemonics used throughout this manual