12-5

IM 2553A-01EN

Status Reports

3

2

1

4

5

6

7

8

9

10

11

12

13

14

App

Index

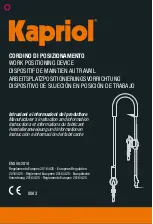

12.4 Extended Event Register

The extended event register receives information about changes in the condition register, which

indicates the instrument's internal condition. The information is the result of edge detection performed

by the transition filter.

6

7

5

4

3

2

1

0

8

9

10

11

12

13

14

15

6

7

5

4

3

2

1

0

8

9

10

11

12

13

14

15

Condition register

:STATus:CONDition?

Transition filter

0

14

15

Extended event register

1

6

7

5

4

3

8

9

10

11

12

13

2

6

7

5

4

3

2

1

8

9

10

11

12

13

14

15

16

:STATus:FILTer<x>

{RISE│FALL│BOTH│NEVer}

:STATus:EESR?

FILTer<x>

0

0

0

IRJC SCG ERJC OUT

0

0

OSC

0

0

VLMT

ILMT

CID

RJON

The condition register bits are described below.

Bit 0

‒

Always 0

Bit 1

OUT

(Output On)

Set to 1 when output is on.

Bit 2

ERJC

(External Rjc Valid)

Set to 1 when the measured value of the external reference junction is

within the measurement range.

Bit 3

SCG

(Source Change)

Set to 1 when the output is turned on or the output setting is changed and

changes to 0 after approximately 500 ms.

Bit 4

IRJC

(Internal Rjc Valid)

Set to 1 when the measured value of the internal reference junction is

within the measurement range.

Bit 5

‒

Always 0

Bit 6

‒

Always 0

Bit 7

‒

Always 0

Bit 8

‒

Always 0

Bit 9

‒

Always 0

Bit 10

‒

Always 0

Bit 11

OSC

(Oscillating)

Set to 1 when an amplifier oscillation error is detected.

Bit 12

VLMT

(Voltage Limiting)

Set to 1 when an overvoltage load is detected.

Bit 13

ILMT

(Current Limiting)

Set to 1 when an overcurrent load is detected.

Bit 14

CID

(Current Input Detected)

Set to 1 when an excessive current input is detected.

Bit 15

RJON

(RJ Connect)

Set to 1 when an external reference junction (RJ) sensor is connected.

The transition filter parameters detect changes in the specified condition register bits (numeric suffixes

1 to 16) and overwrite the extended event register in the following ways.

RISE

The specified extended event register bit is set to 0 when the corresponding condition register bit

changes from 0 to 1.

FALL

The specified extended event register bit is set to 1 when the corresponding condition register bit

changes from 1 to 0.

BOTH

The specified extended event register bit is set to 1 when the corresponding condition register bit

changes from 0 to 1 or from 1 to 0.

NEVer

Always zero.