23

DTXTREME

Ⅲ

211

212

213

214

215

216

217

218

219

220

221

222

223

224

225

226

227

228

229

230

231

232

233

234

235

236

237

238

239

240

241

242

243

244

245

246

247

248

249

250

251

252

253

254

255

256

257

258

259

260

261

262

263

264

265

266

267

268

269

270

271

272

273

274

275

276

277

278

279

280

281

282

283

284

285

286

287

288

289

290

291

292

293

294

295

296

297

298

299

300

301

302

303

304

305

306

307

308

309

310

311

312

313

314

315

VSS

VDD1

DMAL1

DCSL2

DRAS0

DCAS0

VDD3

DCLKIN

DQML2

DCSL3

DQML0

VDD3

VSS

DWEN0

DCLK0

DCLK1

DCLKE

HMD13

VSS

VDD3

HMD15

HMD14

HMD10

HMD12

VDD1

VDD3

HMD7

HMD11

HMD9

HMD8

VSS

VDD1

HMD4

HMD6

HMD5

HMD3

VSS

VSS

HMD1

HMD2

HMD0

DCSH0

VSS

VDD3

DCSH1

DQMH3

DQMH1

DMAH14

DMAH13

VSS

VSS

DMAH11

DMAH12

DMAH10

DMAH9

DMAH8

VDD3

VDD3

DMAH6

DMAH7

DMAH4

DMAH3

VDD3

VSS

DMAH5

DMAH2

DMAH1

DMAH0

VSS

VSS

DRAS1

DCSH2

DQMH2

DCSH3

VDD1

VSS

DQMH0

DWEN1

DCAS1

DCLK2

VDD3

VDD1

DCLK3

MELO0

MELO1

MELO2

VDD3

VSS

MELO3

MELO4

MELO5

MELO6

MELO7

WCLK0

WCLK1

EIRQ

EICN

ESDA

ESCL

MELI0

MELI1

MELI2

MELI3

MELI4

MELI5

-

-

O

O

O

O

-

I

O

O

O

-

-

O

O

O

O

I/O

-

-

I/O

I/O

I/O

I/O

-

-

I/O

I/O

I/O

I/O

-

-

I/O

I/O

I/O

I/O

-

-

I/O

I/O

I/O

O

-

-

O

O

O

O

O

-

-

O

O

O

O

O

-

-

O

O

O

O

-

-

O

O

O

O

-

-

O

O

O

O

-

-

O

O

O

O

-

-

O

O

O

O

-

-

O

O

O

O

O

O

O

O

O

I/O

I/O

I

I

I

I

I

I

Ground

Power 1.5 V

Address bus (DIMM, SDRAM)

Wave memory chip select (Low)

DIMM, SDRAM row address strobe (RAS signal)

DIMM, SDRAM column address strobe (CAS signal)

Power 3.3 V

DIMM, SDRAM clock input

MASK signal

Wave memory chip select (Low)

MASK signal

Power 3.3 V

Ground

DIMM, SDRAM write enable

DIMM, SDRAM clock signal

DIMM, SDRAM clock enable

Wave memory data bus (Upper data memory)

Ground

Power 3.3 V

Wave memory data bus (Upper data memory)

Power 1.5 V

Power 3.3 V

Wave memory data bus (Upper data memory)

Ground

Power 1.5 V

Wave memory data bus (Upper data memory)

Ground

Ground

Wave memory data bus (Upper data memory)

Wave memory chip select (High)

Ground

Power 3.3 V

Wave memory chip select (High)

MASK signal

Address bus (DIMM, SDRAM)

Ground

Ground

Address bus (DIMM, SDRAM)

Power 3.3 V

Power 3.3 V

Address bus (DIMM, SDRAM)

Power 3.3 V

Ground

Address bus (DIMM, SDRAM)

Ground

Ground

DIMM, SDRAM row address strobe (RAS signal)

Wave memory chip select (High)

MASK signal

Wave memory chip select (High)

Power 1.5 V

Ground

MASK signal

DIMM, SDRAM write enable

DIMM, SDRAM column address strobe (CAS signal)

DIMM, SDRAM clock signal

Power 3.3 V

Power 1.5 V

DIMM, SDRAM clock signal

MEL wave data output

Power 3.3 V

Ground

MEL wave data output

For DAC word clock

E bus interrupt request

E bus initial clear

E bus data

E bus clock

MEL wave data input

316

317

318

319

320

321

322

323

324

325

326

327

328

329

330

331

332

333

334

335

336

337

338

339

340

341

342

343

344

345

346

347

348

349

350

351

352

353

354

355

356

357

358

359

360

361

362

363

364

365

366

367

368

369

370

371

372

373

374

375

376

377

378

379

380

381

382

383

384

385

386

387

388

389

390

391

392

393

394

395

396

397

398

399

400

401

402

403

404

405

406

407

408

409

410

411

412

413

414

415

416

417

418

419

420

AB22

AC23

AD24

AE25

AF26

AC22

AB21

AD23

AE24

AF25

AF24

AC21

AB20

AD22

AE23

AF23

AC20

AD21

AB19

AC19

AE22

AF22

AD20

AE21

AB18

AC18

AD19

AF21

AE20

AF20

AB17

AC17

AD18

AE19

AF19

AE18

AB16

AC16

AD17

AF18

AE17

AF17

AB15

AC15

AD16

AE16

AF16

AD15

AE15

AB14

AC14

AD14

AF15

AE14

AF14

AF13

AB13

AC13

AD13

AE13

AE12

AD12

AC12

AB12

AF12

AF11

AE11

AD11

AC11

AB11

AF10

AE10

AF9

AD10

AC10

AB10

AE9

AF8

AD9

AE8

AC9

AB9

AD8

AF7

AE7

AD7

AC8

AB8

AF6

AE6

AF5

AC7

AD6

AB7

AC6

AE5

AF4

AD5

AE4

AB6

AC5

AD4

AF3

AE3

AF2

AB5

AC4

AD3

AE2

AF1

AB4

AA5

AC3

AD2

AE1

AD1

AA4

Y5

AB3

AC2

AC1

Y4

AA3

W5

W4

AB2

AB1

Y3

AA2

V5

V4

W3

AA1

Y2

Y1

U5

U4

V3

W2

W1

V2

T5

T4

U3

V1

U2

U1

R5

R4

T3

T2

T1

R3

R2

P5

P4

P3

R1

P2

P1

N1

N5

N4

N3

N2

M2

M3

M4

M5

M1

L1

L2

L3

L4

L5

K1

K2

J1

K3

K4

K5

J2

H1

J3

H2

J4

J5

H3

G1

G2

G3

H4

H5

F1

F2

E1

G4

F3

G5

F4

E2

D1

E3

D2

F5

E4

D3

C1

C2

B1

VSS

VDD1

MELI6

MELI7

ADLR

DITo

VSS

AFRM

ACLK

ADIR

ADAT0

VDD3

ADAT9

ADAT3

ADAT1

ADAT2

ADAT10

ADAT6

VSS

VDD3

ADAT4

ADAT5

ADAT11

ADAT7

ADAT14

ADAT15

ADAT13

ADAT8

ADAT12

TDI

VSS

VDD1

HRD13

HRD15

HRD14

HRD12

HRD7

HRD6

HRD10

HRD11

HRD9

HRD8

VSS

VDD3

HRD5

HRD4

HRD3

HRD2

HRD1

VDD3

HRD0

RWEN

RQML

RCAS

RRAS

RA13

VDD3

VDD3

RA10

RA12

RA1

RA2

VDD3

VSS

RA0

RA3

RA4

RA5

VSS

VSS

RA6

RA7

RA9

RA8

VDD1

VSS

RA11

RCLK

RCLKE

RCLKIN

VDD3

VDD1

RQMH

LRD15

LRD14

LRD13

VDD3

VSS

LRD12

LRD11

LRD8

VDD3

LRD10

VDD3

LRD9

LRD7

LRD5

LRD6

LRD4

VSS

VSS

LRD3

LRD2

LRD1

LRD0

-

-

I

I

O

O

-

I/O

I/O

O

I/O

-

I/O

I/O

I/O

I/O

I/O

I/O

-

-

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I

-

-

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

I/O

-

-

I/O

I/O

I/O

I/O

I/O

-

I/O

O

O

O

O

O

-

-

O

O

O

O

-

-

O

O

O

O

-

-

O

O

O

O

-

-

O

O

O

I

-

-

O

I/O

I/O

I/O

-

-

I/O

I/O

I/O

-

I/O

-

I/O

I/O

I/O

I/O

I/O

-

-

I/O

I/O

I/O

I/O

Ground

Power 1.5 V

MEL wave data input

For ADC word clock

Digital audio output

Ground

Frame signal (ABUS)

Clock signal (ABUS)

Direction signal (ABUS)

Data bus (ABUS)

Power 3.3 V

Data bus (ABUS)

Ground

Power 3.3 V

Data bus (ABUS)

Test pin

Ground

Power 1.5 V

DRAM data bus

Ground

Power 3.3 V

DRAM data bus

Power 3.3 V

DRAM data bus

DRAM write enable

MASK signal (SDRAM)

DRAM column address strobe (CAS signal)

DRAM row address strobe (RAS signal)

DRAM address bus

Power 3.3 V

Power 3.3 V

DRAM address bus

Power 3.3 V

Ground

DRAM address bus

Ground

Ground

DRAM address bus

Power 1.5 V

Ground

DRAM address bus

SDRAM clock signal

SDRAM clock enable

SDRAM, DRAM clock input

Power 3.3 V

Power 1.5 V

MASK signal (SDRAM)

DRAM data bus (Lower data)

Power 3.3 V

Ground

DRAM data bus (Lower data)

Power 3.3 V

DRAM data bus (Lower data)

Power 3.3 V

DRAM data bus (Lower data)

Ground

Ground

DRAM data bus (Lower data)

PIN

NO.

OUTER

NO.

NAME

I/O

FUNCTION

PIN

NO.

OUTER

NO.

NAME

I/O

FUNCTION

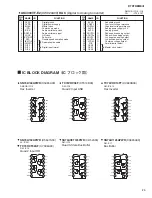

Summary of Contents for DTXTREME III

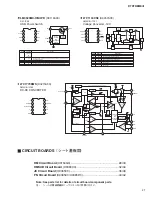

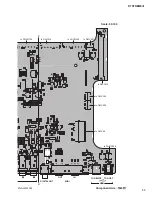

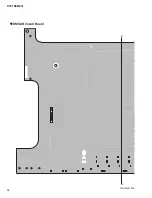

Page 30: ...DTXTREMEⅢ 30 B B DM Circuit Board 2NA WJ91030 2 ...

Page 31: ...31 DTXTREMEⅢ B B Pattern side パターン側 2NA WJ91030 2 ...

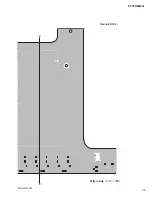

Page 34: ...DTXTREMEⅢ 34 D D DMSUB Circuit Board 2NA WJ91040 ...

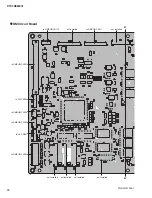

Page 35: ...35 DTXTREMEⅢ D D Pattern side パターン側 Scale 85 100 2NA WJ91040 ...

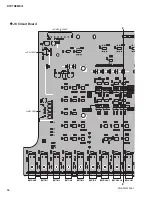

Page 38: ...DTXTREMEⅢ 38 F F JK Circuit Board 2NA WJ91050 2 ...

Page 39: ...39 DTXTREMEⅢ F F Pattern side パターン側 Scale 95 100 2NA WJ91050 2 ...

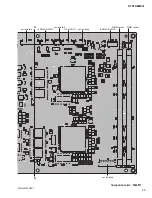

Page 42: ...DTXTREMEⅢ 42 H H or D PN Circuit Board 2NA WJ91060 2 ...

Page 43: ...43 DTXTREMEⅢ H H Pattern side パターン側 Scale 80 100 2NA WJ91060 2 ...