W25Q16BV

Publication Release Date: July 08, 2010

- 65 - Revision F

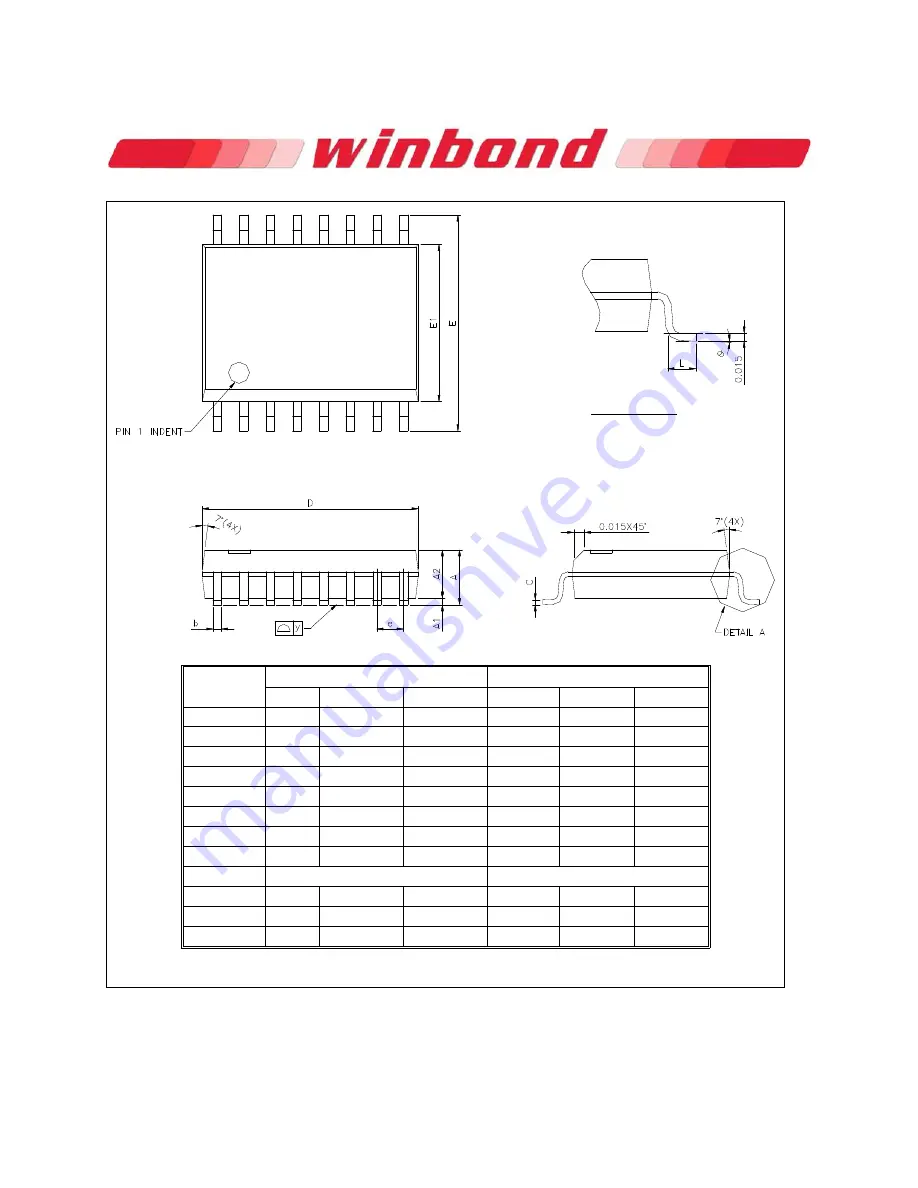

13.5

16-Pin SOIC 300-mil (Package Code SF)

GAUGE PLANE

DETAIL A

GAUGE PLANE

DETAIL A

MILLIMETERS INCHES

SYMBOL

Min Nom Max Min Nom Max

A 2.36

2.49 2.64 0.093

0.098

0.104

A1 0.10 ---

0.30 0.004 --- 0.012

A2 --- 2.31 --- --- 0.091 ---

b 0.33

0.41 0.51 0.013

0.016

0.020

C 0.18 0.23 0.28 0.007

0.009

0.011

D 10.08

10.31 10.49 0.397 0.406 0.413

E 10.01

10.31 10.64 0.394 0.406 0.419

E1 7.39 7.49 7.59 0.291 0.295 0.299

e

(2)

1.27 BSC.

0.050 BSC.

L 0.38

0.81 1.27 0.015

0.032

0.050

y --- --- 0.076 --- --- 0.003

θ

0° ---

8° 0° --- 8°

Notes:

1. Controlling dimensions: inches, unless otherwise specified.

2. BSC = Basic lead spacing between centers.

3. Dimensions D and E1 do not include mold flash protrusions and should be measured from the bottom of the package.