9

4

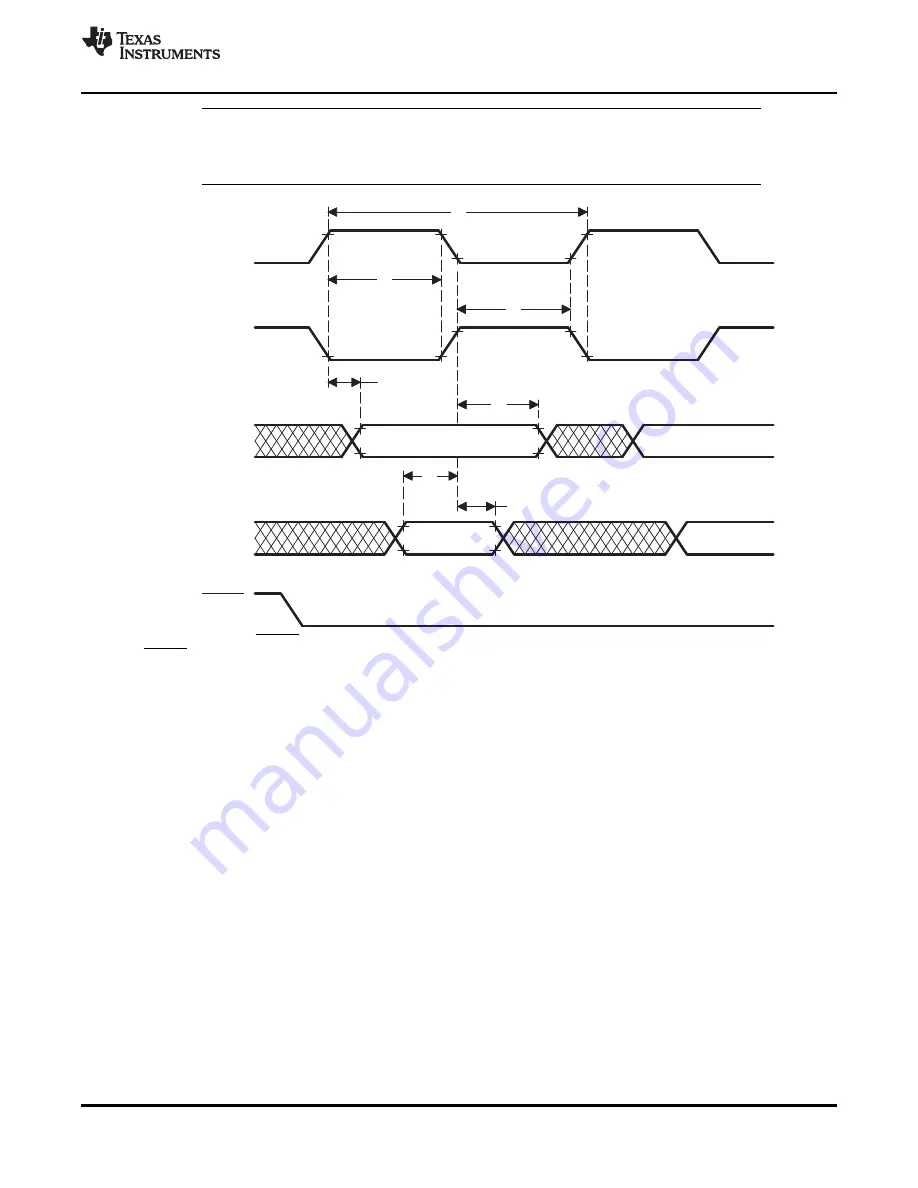

SPISOMI

SPISIMO

SPICLK

(clock polarity = 1)

SPICLK

(clock polarity = 0)

Master In Data

Must Be Valid

Master Out Data Is Valid

8

5

3

2

1

SPISTE

(see Note A)

SM320F2812-HT

www.ti.com

SGUS062B

–

JUNE 2009

–

REVISED JUNE 2011

NOTE

Internal clock prescalers must be adjusted such that the SPI clock speed is not greater than

the I/O buffer speed limit (20 MHz).

A.

In the master mode, SPISTE goes active 0.5tc(SPC) before valid SPI clock edge. On the trailing end of the word, the

SPISTE will go inactive 0.5tc(SPC) after the receiving edge (SPICLK) of the last data bit.

Figure 6-24. SPI Master Mode External Timing (Clock Phase = 0)

Copyright

©

2009

–

2011, Texas Instruments Incorporated

Electrical Specifications

109

Submit Documentation Feedback

Product Folder Link(s):

SM320F2812-HT

Summary of Contents for SM320F2812-HT Data

Page 152: ......