SM320F2812-HT

www.ti.com

SGUS062B

–

JUNE 2009

–

REVISED JUNE 2011

Enhanced feature:

•

16-level transmit/receive FIFO

•

Delayed transmit control

The SPI port operation is configured and controlled by the registers listed in

Table 4-10

.

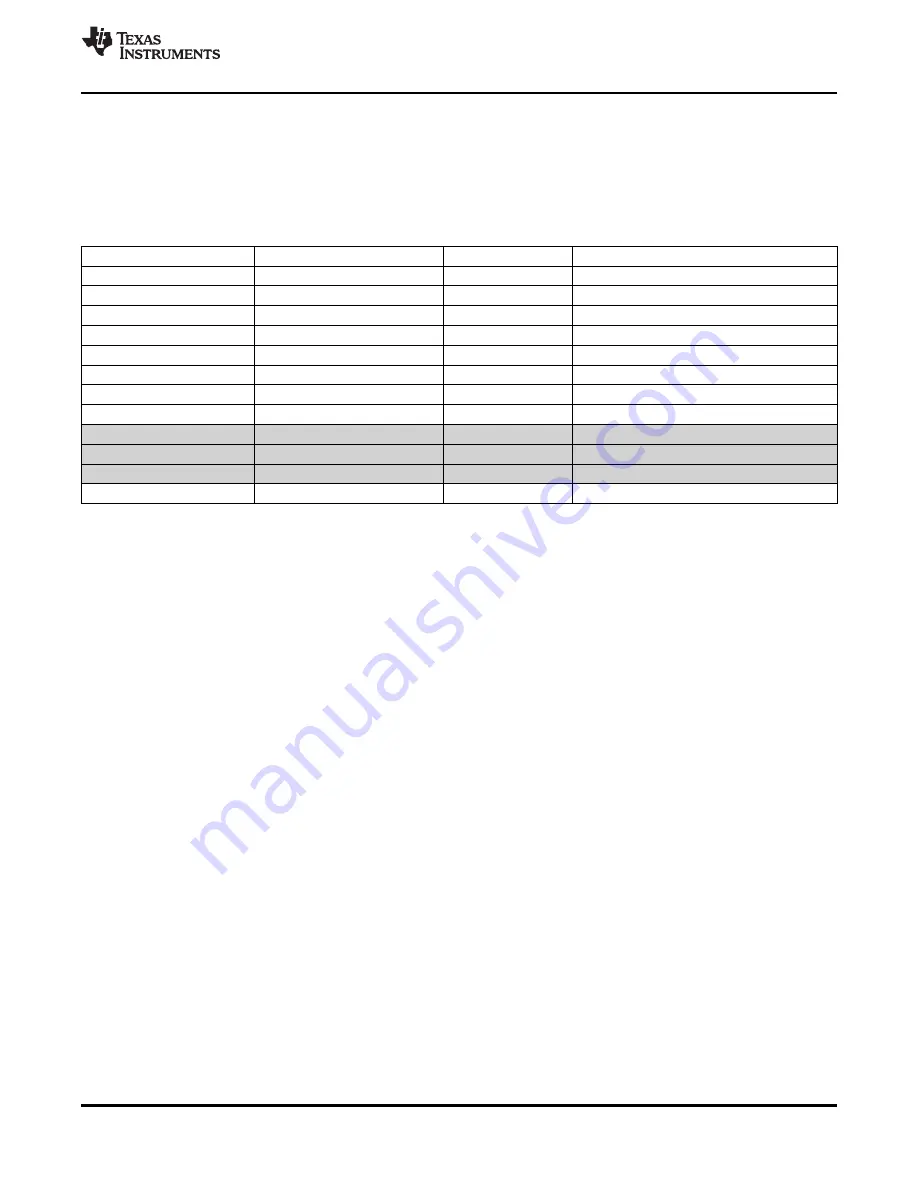

Table 4-10. SPI Registers

(1)

NAME

ADDRESS

SIZE (

×

16)

DESCRIPTION

SPICCR

0x00 7040

1

SPI Configuration Control Register

SPICTL

0x00 7041

1

SPI Operation Control Register

SPISTS

0x00 7042

1

SPI Status Register

SPIBRR

0x00 7044

1

SPI Baud Rate Register

SPIRXEMU

0x00 7046

1

SPI Receive Emulation Buffer Register

SPIRXBUF

0x00 7047

1

SPI Serial Input Buffer Register

SPITXBUF

0x00 7048

1

SPI Serial Output Buffer Register

SPIDAT

0x00 7049

1

SPI Serial Data Register

SPIFFTX

0x00 704A

1

SPI FIFO Transmit Register

SPIFFRX

0x00 704B

1

SPI FIFO Receive Register

SPIFFCT

0x00 704C

1

SPI FIFO Control Register

SPIPRI

0x00 704F

1

SPI Priority Control Register

(1)

The above registers are mapped to Peripheral Frame 2. This space only allows 16-bit accesses. 32-bit accesses produce undefined

results.

Copyright

©

2009

–

2011, Texas Instruments Incorporated

Peripherals

75

Submit Documentation Feedback

Product Folder Link(s):

SM320F2812-HT

Summary of Contents for SM320F2812-HT Data

Page 152: ......