Test Setup and Results

www.ti.com

14

SLLU298 – May 2018

Submit Documentation Feedback

Copyright © 2018, Texas Instruments Incorporated

ISO5852SDW Driving and Protecting SiC and IGBT Power Modules

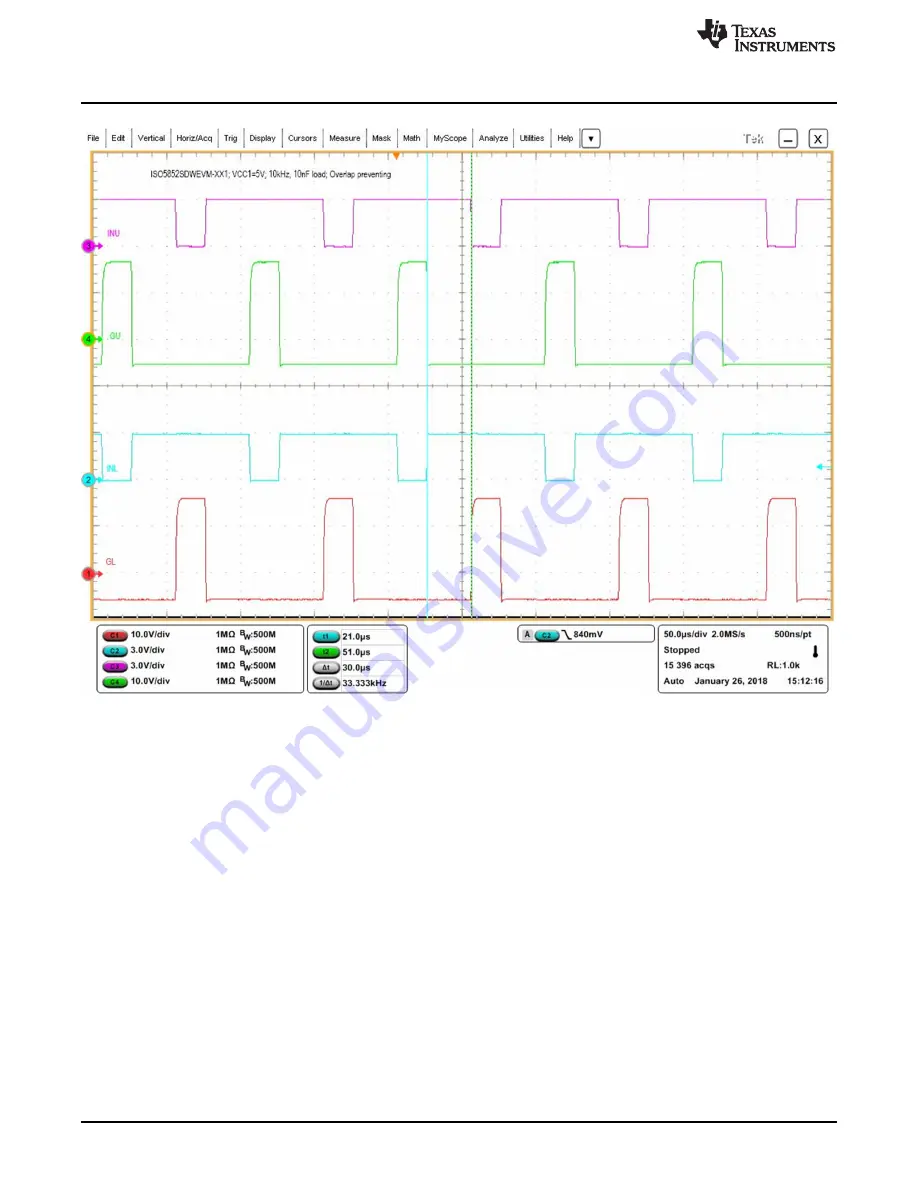

Figure 6. Major Input and Output Waveforms Using Output Overlapping Prevention Feature

•

INU (pink) is high side input: 3.0V/div

•

OU (green) is high side output: 10V/div

•

INL (blue) is low side input: 3.0V/div

•

OL (red) is low side output: 10V/div

•

Time scale is 50µs/div