7.5.2.2 I

2

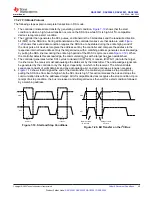

C Update Sequence

shows that for a single update, the DACx300x require a start condition, a valid I

2

C address byte, a

command byte, and two data bytes.

Table 7-14. Update Sequence

MSB

....

LSB

ACK

MSB

...

LSB

ACK

MSB

...

LSB

ACK

MSB

...

LSB

ACK

Address (A) byte

Command byte

Data byte - MSDB

Data byte - LSDB

DB [31:24]

DB [23:16]

DB [15:8]

DB [7:0]

shows that after each byte is received, the DACx300x family acknowledges the byte by pulling the

SDA line low during the high period of a single clock pulse. These four bytes and acknowledge cycles make up

the 36 clock cycles required for a single update to occur. A valid I

2

C address byte selects the DACx300x.

1

7

8

9

1

2 - 8

9

S

or

Sr

SDA

SCL

MSB

Address

START or

REPEATED

START

condition

Recognize

START or

REPEATED

START

condition

R/W

ACK

Acknowledgement

signal from target

Generate ACKNOWLEDGE

signal

Sr

or

P

P

Sr

REPEATED

START or

STOP

condition

Recognize

STOP or

REPEATED

START

condition

ACK

Figure 7-21. I

2

C Bus Protocol

The command byte sets the operating mode of the selected DACx300x device. For a data update to occur

when the operating mode is selected by this byte, the DACx300x device must receive two data bytes: the most

significant data byte (MSDB) and least significant data byte (LSDB). The DACx300x device performs an update

on the falling edge of the acknowledge signal that follows the LSDB.

When using fast mode (clock = 400 kHz), the maximum DAC update rate is limited to 10 kSPS. Using fast mode

plus (clock = 1 MHz), the maximum DAC update rate is limited to 25 kSPS. When a stop condition is received,

the DACx300x device releases the I

2

C bus and awaits a new start condition.

DAC53001, DAC53002, DAC63001, DAC63002

SLASF48 – MAY 2022

50

Copyright © 2022 Texas Instruments Incorporated

Product Folder Links: