6.6 Programming Spread Spectrum

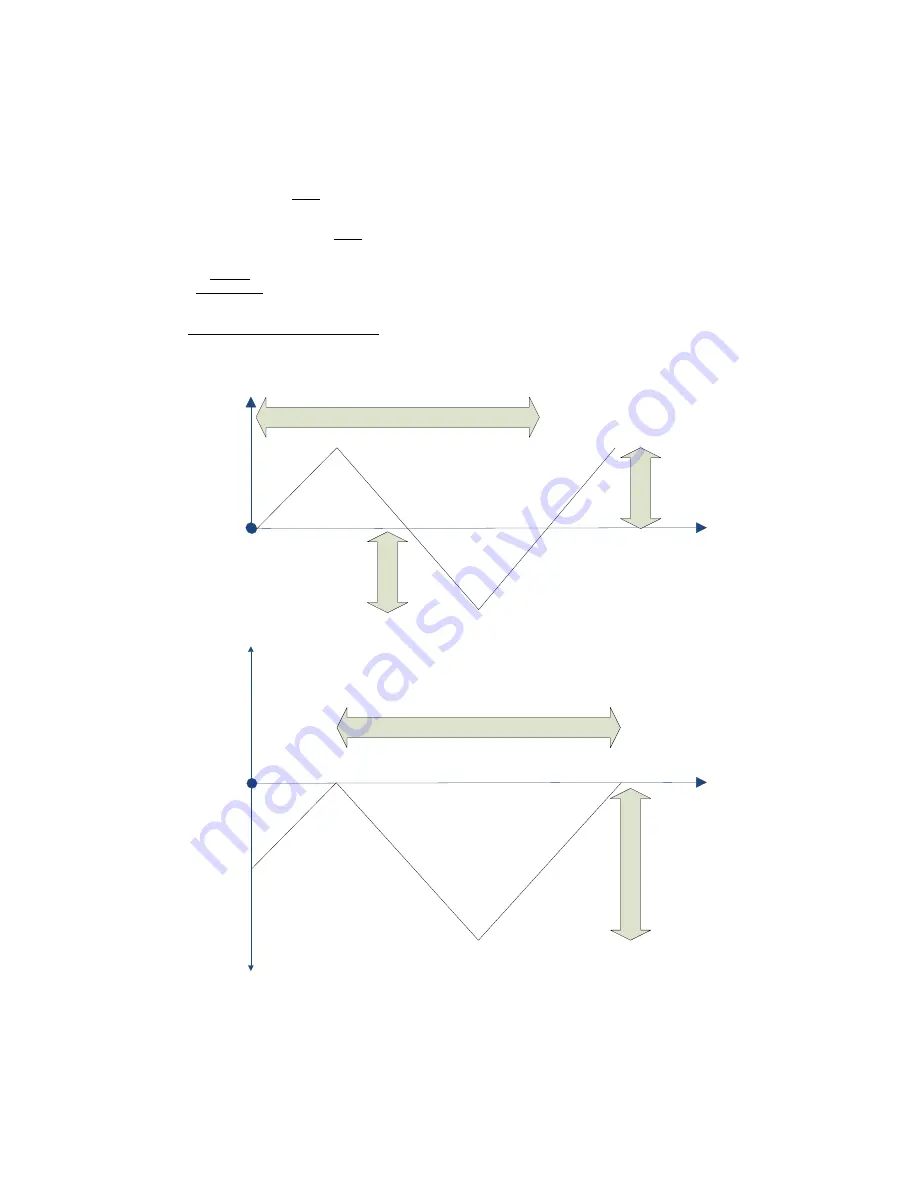

Spread spectrum clocking (SSC) is available only on the Multisynth outputs. Each Multisynth can implement spread spectrum in

either the main divider or the backup divider (the FS option). Therefore, the user can program a maximum of four different spread

spectrum “profiles” from the same part, although only two profile are available on outputs at any given time. The amplitude of the SSC

clock frequency (as illustrated in the figure below) is denoted by ssc%. The variable, Amod, in the equation below is a real number

representation of the ssc%, which is a percentage value. For example, for down spread of -0.5%, then ssc% = 0.5. For center spread of

+/- 0.25%, then ssc% = 0.25. The modulation rate (also illustrated in the figure below) is denoted by Fmod in the equations below.

For Down Spread:

Amod

=

ssc %

100

For Center Spread:

Amod

= 2 ×

ssc %

100

idxy_ss_step_num =

vcoFreq

idxy

Fmod × 4

idxy_ss_step_res =

Amod × idxy_den × idxy × 128

2 × idxy_ss_step_num

time

frequency

F0

Fmax = F0 (1 + ssc%/100)

Fmin = F0 (1 - ssc%/100)

Fmod = one modulation cycle

Fmod = one modulation cycle

F0

frequency

time

Fmin = F0 (1 - ssc%/100)

Figure 6.2. Center and Down Spread SSC Clocks as Frequency vs Time

Si5332-AM1/2/3 Automotive Grade Device Reference Manual • Programming the Volatile Memory (Registers)

Skyworks Solutions, Inc. • Phone [781] 376-3000 • Fax [781] 376-3100 • [email protected] • www.skyworksinc.com

27

Rev. 0.3 • Skyworks Proprietary Information • Products and Product Information are Subject to Change Without Notice • July 26, 2021

27