65

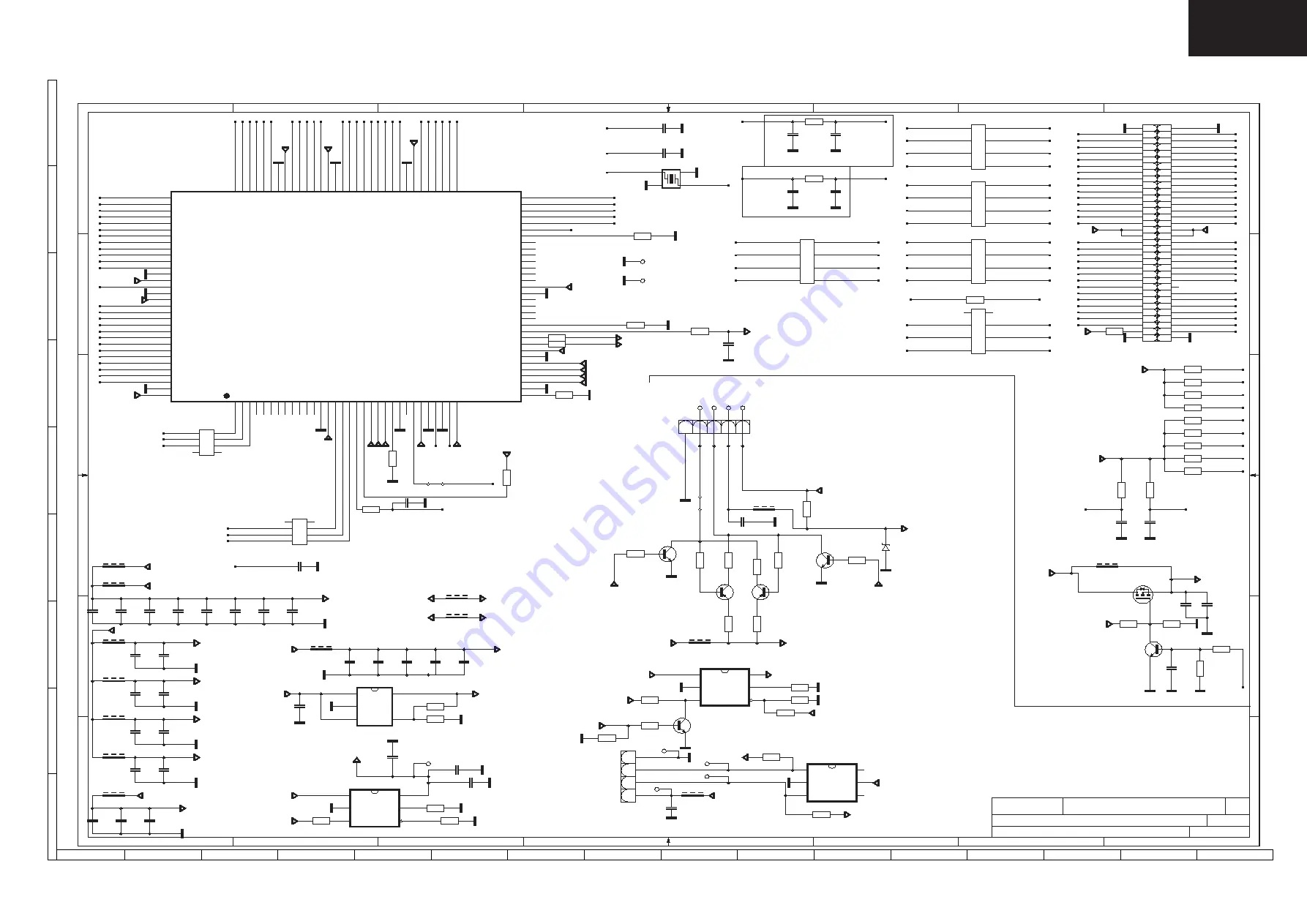

LC-32LD145

LC-39LD145

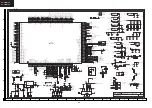

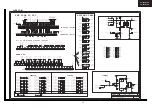

SCHEMATIC DIAGRAMS

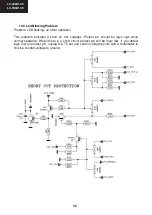

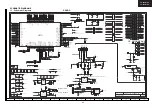

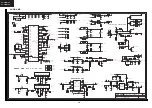

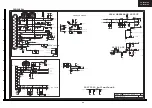

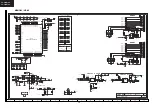

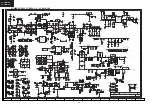

15 . Schematic Diagrams DEMOD

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

I

H

G

F

E

D

C

B

A

R2002

22R

1

2

3

4

5

6

7

8

R2

R3

R1

R4

22R

R2001

8

7

6

5

4

3

2

1

R2

R3

R1

R4

R2003

22R

1

2

3

4

5

6

7

8

R2

R3

R1

R4

22R

R2004

1

2

3

4

5

6

7

8

R2

R3

R1

R4

R2005

22R

1

2

3

4

5

6

7

8

R2

R3

R1

R4

R2008

680R

R2010

4k7

2

1

16V

C712

100n

680R

R2009

U40

TPS2553-1

4

5

6

3

2

1 IN

GND

EN

OUT

ILIM

FAULT

TP200

1

C713

100p

50V

ACT_ANT

16V

10u

C714

F189

1k

U3

TLV71209

5

4

3

2

1 IN

GND

EN

N/C

OUT

TP122

TP121

TP120

TP119

CN18

5

4

3

2

1

LBS

LBS

MXL601_SCL

MXL601_SDA

R2101

10k

2

1

5135_IF_P

5135_IF_N

100n

10V

C1116

Q34

BC848B

R2069

560R

5V_VCC

60R

F186

U45

AZ099-04S

6

5

4

3

2

1 IO1

GND

IO2

IO3

VDD

IO4

U44

TPS2553-1

4

5

6

3

2

1 IN

GND

EN

OUT

ILIM

FAULT

33RR2129

5V_VCC

14-12-2012_14:59

DEMOD

9

<YOUR NAME HERE>

17mb82-1a

8

7

6

5

4

3

2

1

A

B

C

D

E

F

A X M

1

2

3

4

5

6

7

8

A

B

C

D

E

F

A3

PROJECT NAME :

VESTEL

SCH NAME :

DRAWN BY :

T. SHT:

5V_STBY

S17

2

1

220R

R474

2

1

10k

R74

2

1

BC848B

Q5

3

2

1

R73

10k

2

1

R72

10k

2

1

Q4

BC848B

3

2

1

10k

R71

2

1

50V

C1

27p

2

1

R2070

560R

1k

F60

R473

220R

2

1

BC858B

Q40

3

2

1

R70

10k

2

1

BC858B

Q39

3

2

1

220R

R472

2

1

10V

C118

100n

USB1_VCC

3V3_VCC

10k

R2118

TP209

X5

27MHz

2

4

1

3

27p

C179

2

1

R471

220R

2

1

TP107

CN6

68

67

66

65

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

100n

C120

10V

10V

C121

100n

10V

100n

C122

10V

C123

100n

10V

100n

C170

TP110

TP210

3V3_VCC

5135_DV33

C5V6

D8

2

1

IF_AGC

C358

47n

16V

R2130

33R

180R

R272

AVDD33_1

27p

C180

2

1

6V3

10u

C1163

Q49

BSH103

470R

R274

1V1_MT5135

CN28

4

3

2

1

5V_VCC

33k

R253

R208

10k

10k

R209

R643

10R

2

1

10R

R644

2

1

USB1_DP

USB1_DM

3V3_VCC

R426

4k7

2

1

USB1_VCC

5V_VCC

R428

4k7

2

1

10k

R2140

5135_DV10

USB1_VCC

C623

16V

10u

5135_AV12

F11

330R

2

1

F2

1k

F96

330R

2

1

33k

R510

C106

10V

100n

2

1

5V_VCC

1V2_AVCC

12V_VCC

1V1_MT5135

10p 50V

C12

C107

100n

10V

10V

100n

C108

USB_ENABLE

VCC_PCMCIA

1V2_MT5820

C582

6V3

10u

AVDD33_4

5135_DV33

33R

R26

8

7

6

5

4

3

2

1

R4

R3

R2

R1

47R

R49

C488

50V

10p

S143

1M

R737

F82

1k

6V3

10u

C577

C119

100n

10V

F83

1k

1k

F85

LED2

LED1

IR_IN

1k

F84

1k

F86

6V3

10u

C578

47k

R449

R450

47k

6V3

C579

10u

C580

6V3

10u

C1207

100n

10V

BC848B

Q222

3

2

1

R2096

10k

2

1

100n

10V

C124

100n

10V

C125

100n

10V

C126

10V

C127

100n

AVDD33_1

AVDD33_2

AVDD33_3

AVDD33_4

AVDD33_1

AVDD33_2

AVDD33_3

1k

F90

5135_DV33

5135_DV10

10u

C583

6V3

100n

10V

C128

4k7

R758

5135_DV33

100n

10V

C129

4k7

R759

5135_DV33

5135_DV33

5135_DV33

R51

47R

MT5135

U15

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

96

95

94

93

92

91

90

89

88

87

86

85

84

83

82

81

80

79

78

77

76

75

74

73

72

71

70

69

68

67

66

65

128

127

126

125

124

123

122

121

120

119

118

117

116

115

114

113

112

111

110

109

108

107

106

105

104

103

102

101

100

99

98

97

A15

A24

A12

A25

A7

VS2_

A6

PCMCIA_RESET

A5

WAIT_

A4

A3

DVSS_6

DVDD33_4

REG_

DVSS_7

DVDD10_3

A2

BVD2

A1

BVD1

A0

D8

D0

D9

D1

D10

D2

CD2_

CI_INT

DVSS_8

DVDD33_5

D13

D6

D14

D7

D15

CE1_

DVDD33_2

DVSS_3

A10

VS1_

OE_

IORD_

A11

IOWR_

A9

A17

A8

DVSS_4

DVDD10_2

A18

A13

A19

A14

A20

DVDD33_3

DVSS_5

WE_

A21

READY

A22

A16

A23

D5

D12

D4

D11

D3

CD1_

CHIP_CTRL

S2_TS_DATA7

S2_TS_DATA6

S2_TS_DATA5

S2_TS_DATA4

S2_TS_DATA3

S2_TS_DATA2

S2_TS_DATA1

DVDD33_1

DVSS_2

S2_TS_DATA0

S2_TS_VAL

S2_TS_SYNC

S2_TS_CLK

RF_AGC

IF_AGC

TUNER_CLK

TUNER_DATA

DVDD10_1

DVSS_1

AVDD33_IFPGA

AVDD12_DEMOD

IFPGA_INP

IFPGA_INN

AVSS12_DEMOD

EXT_CLKSEL

AVDD33_XTAL

XTALO

AVSS33_XTAL

XTALI

AVSS33_DEMOD

AVDD33_DEMOD

TP

TN

AVSS33_RSSI

ADIN0

AVDD33_RSSI

AVDD12_PLL

DVDD10

MT5135_RST_B

DEMOD_TS_CLK

DEMOD_TS_VAL

DEMOD_TS_SYNC

DEMOD_TS_DATA0

DVDD33

DVSS

CI_TS_CLK

CI_TS_VAL

CI_TS_SYNC

CI_TS_DATA0

PVR_TS_CLK

PVR_TS_VAL

PVR_TS_SYNC

PVR_TS_DATA0

PVR_TS_DATA1

SPI_CLK

SPI_DATA

SPI_CLE

TP198

TP199

33R

R2094

8

7

6

5

4

3

2

1

R4

R3

R2

R1

47R

R50

50V

C489

10p

C490

50V

10p

10k

R201

R202

10k

R203

10k

C130

10V

100n

C131

100n

10V

10k

R204

5135_DV33

10k

R196

R197

10k

R198

10k

10V

C132

100n

5135_AV12

5135_DV10

5135_AV12

5135_DV10

5135_DV10

5135_DV10

VCC_PCMCIA

VCC_PCMCIA

1V2_AVCC

VCC_PCMCIA

5135_AV12

100n

C133

10V

50V

C491

10p

10p

C492

50V

C134

100n

10V

R199

10k

R200

10k

R205

10k

R206

10k

VCC_PCMCIA

10k

R207

3V3_AVCC

F81

1k

3V3_AVCC

1k

F87

M_CI_OUTDATA5

M_CI_OUTDATA5

M_CI_INVALID

M_CI_INVALID

CI_IREQ#

CI_IREQ#

CI_IREQ#

M_CI_INDATA3

M_CI_INDATA3

M_CI_INDATA4

M_CI_INDATA4

CI_WE#

CI_WE#

CI_WE#

M_CI_INDATA2

M_CI_INDATA2

CI_A14

CI_A14

M_CI_INDATA1

M_CI_INDATA1

CI_A13

CI_A13

M_CI_INDATA0

M_CI_INDATA0

CI_A8

CI_A8

M_CI_INSYNC

M_CI_INSYNC

CI_A9

CI_A9

CI_IOWR#

CI_IOWR#

CI_IOWR#

CI_A11

CI_A11

CI_IORD#

CI_IORD#

CI_IORD#

CI_OE#

CI_OE#

CI_OE#

CI_A10

CI_A10

M_CI_OUTDATA7

M_CI_OUTDATA7

CI_D7

CI_D7

M_CI_OUTDATA6

M_CI_OUTDATA6

CI_D6

CI_D6

M_CI_INDATA5

M_CI_INDATA5

M_CI_INDATA6

M_CI_INDATA6

CI_A12

CI_A12

M_CI_INDATA7

M_CI_INDATA7

CI_A7

CI_A7

M_CI_OUTCLK

M_CI_OUTCLK

CI_A6

CI_A6

CI_RESET

CI_RESET

CI_A5

CI_A5

CI_WAIT#

CI_WAIT#

CI_WAIT#

CI_A4

CI_A4

CI_A3

CI_A3

CI_REG#

CI_REG#

CI_A2

CI_A2

M_CI_OUTVALID

M_CI_OUTVALID

CI_A1

CI_A1

M_CI_OUTSYNC

M_CI_OUTSYNC

CI_A0

CI_A0

M_CI_OUTDATA0

M_CI_OUTDATA0

CI_D0

CI_D0

M_CI_OUTDATA1

M_CI_OUTDATA1

M_CI_INCLK

M_CI_INCLK

M_CI_OUTDATA4

M_CI_OUTDATA4

CI_D4

CI_D4

M_CI_OUTDATA3

M_CI_OUTDATA3

CI_D3

CI_D3

CI_D5

CI_D5

DEMOD_TSVAL

DEMOD_TSVAL

DEMOD_TSSYNC

DEMOD_TSDATA0

DEMOD_TSCLK

CI_PWR_EN

CI_PWR_EN

RF_AGC_5135

CI_D2

CI_D2

CI_D1

CI_D1

CI_INT

M_CI_OUTDATA2

M_CI_OUTDATA2

CI_INVALID

CI_INVALID

CI_INSYNC

CI_INSYNC

CI_INDATA0

CI_INDATA0

CI_INDATA1

CI_INDATA1

CI_INDATA2

CI_INDATA2

CI_INDATA3

CI_INDATA3

CI_INDATA4

CI_INDATA4

CI_INDATA5

CI_INDATA5

CI_INDATA6

CI_INDATA6

CI_INDATA7

CI_INDATA7

CI_INCLK

CI_INCLK

CI_OUTCLK

CI_OUTCLK

CI_OUTCLK

CI_OUTVALID

CI_OUTVALID

CI_OUTSYNC

CI_OUTSYNC

CI_OUTDATA0

CI_OUTDATA0

CI_OUTDATA1

CI_OUTDATA1

CI_OUTDATA2

CI_OUTDATA2

CI_OUTDATA3

CI_OUTDATA3

CI_OUTDATA4

CI_OUTDATA4

CI_OUTDATA5

CI_OUTDATA5

CI_OUTDATA6

CI_OUTDATA6

CI_OUTDATA7

CI_OUTDATA7

CI_VS1#

CI_VS1#

CI_VS1#

CI_CE1#

CI_CE1#

XTALI

XTALI

XTALI

CI_CE2#

CI_CE2#

CI_CD2#

CI_CD2#

CI_CD2#

CI_CD1#

CI_CD1#

CI_CD1#

DEMOD_RST

SPI_CLK

SPI_DATA

SPI_CLE

LBS

XTALO

XTALO

XTALO

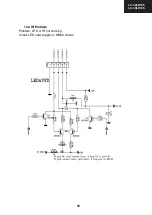

LED&VFD

ANTENNA INPUT

ACTIVE ANTENNA

CI INTERFACE

FC OPT.

TI OPT.

FC pin5 NC, pin6 current limit, R from VCC to pin6 NC

TI pin5 current limit, pin4 fault, R from pin4 to GND NC

1: Differential

0: Single End

close to mt5135

TI OPT.

close to pcmcia

CI girisi ust-altta konacak

nc

NC

Summary of Contents for LC-32LD145K

Page 12: ...12 LC 39LD145 LC 32LD145 English 21 Dimensional Drawings LC39LD145 ...

Page 15: ...15 LC 32LD145 LC 39LD145 3 Remove Speaker Wire 4 Remove AC Cord ...

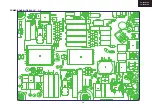

Page 17: ...17 LC 32LD145 LC 39LD145 4 1 1 General Block Diagram 0 1 ...

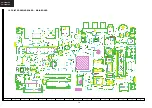

Page 18: ...18 LC 39LD145 LC 32LD145 5 1 2 MB82 Placement of Blocks 0 2 ...

Page 21: ...21 LC 32LD145 LC 39LD145 ...

Page 22: ...22 LC 39LD145 LC 32LD145 ...

Page 23: ...23 LC 32LD145 LC 39LD145 ...

Page 24: ...24 LC 39LD145 LC 32LD145 11 2 4 Pinning ...

Page 25: ...25 LC 32LD145 LC 39LD145 ...

Page 26: ...26 LC 39LD145 LC 32LD145 14 TS4962M optional 2 5W ...

Page 35: ...35 LC 32LD145 LC 39LD145 ...

Page 36: ...36 LC 39LD145 LC 32LD145 ...

Page 38: ...38 LC 39LD145 LC 32LD145 27 x16 Package Pinout Top view 96ball FBGA Package ...

Page 39: ...39 LC 32LD145 LC 39LD145 28 7 SCALER AND LVDS SOCKETS 7 1 LVDS sockets Block Diagram ...

Page 41: ...41 LC 32LD145 LC 39LD145 30 8 1 2 Features 8 1 3 Block Diagram ...

Page 42: ...42 LC 39LD145 LC 32LD145 31 8 1 4 Pinning ...

Page 44: ...44 LC 39LD145 LC 32LD145 33 8 2 3 Block Diagram 8 2 4 Pinning ...

Page 45: ...45 LC 32LD145 LC 39LD145 34 ...

Page 48: ...48 LC 39LD145 LC 32LD145 37 10 3 VGA CN711 10 4 SCART SC1 ...

Page 51: ...51 LC 32LD145 LC 39LD145 11 3 Options Options 1 RET BACK RET BACK Options 2 ...

Page 52: ...52 LC 39LD145 LC 32LD145 11 5 Source Settings 11 4 Tuning Settings RET BACK ...

Page 79: ...79 LC 32LD145 LC 39LD145 POWER BOARD 17IPS20 39 1 2 ...

Page 80: ...80 LC 32LD145 LC 39LD145 POWER BOARD 17IPS20 39 2 2 ...

Page 107: ...107 LC 32LD145 LC 39LD145 ...