S3F84B8_UM_REV 1.00

21 ELECTRICAL DATA

21-7

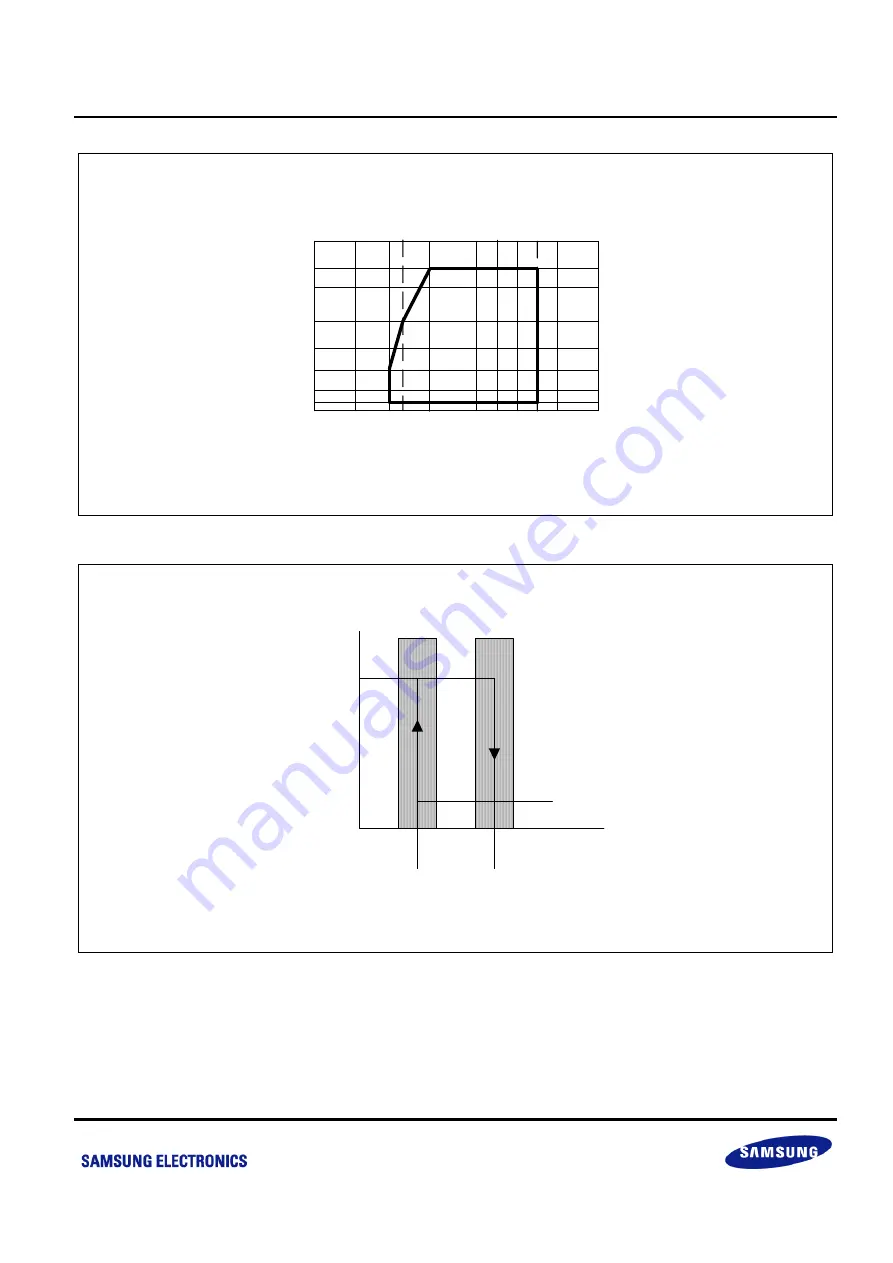

10 MHz

External Clock

Frequency

8 MHz

1 MHz

1

1.8

4

5

6

7

Supply Voltage (V)

2 MHz

3 MHz

4 MHz

..

5.5

4.5

2.7

400KHz

2.0

Figure 21-2 Operating Voltage Range @ External clock

V

SS

A

A = 0.2 V

DD

B = 0.4 V

DD

C = 0.6 V

DD

D = 0.8 V

DD

V

DD

V

OUT

V

IN

B

C

D

0.3 V

DD

0.7 V

DD

Figure 21-3 Schmitt Trigger Input Characteristics Diagram