RTL8201(L)

2002-01-18

Rev.1.04

3

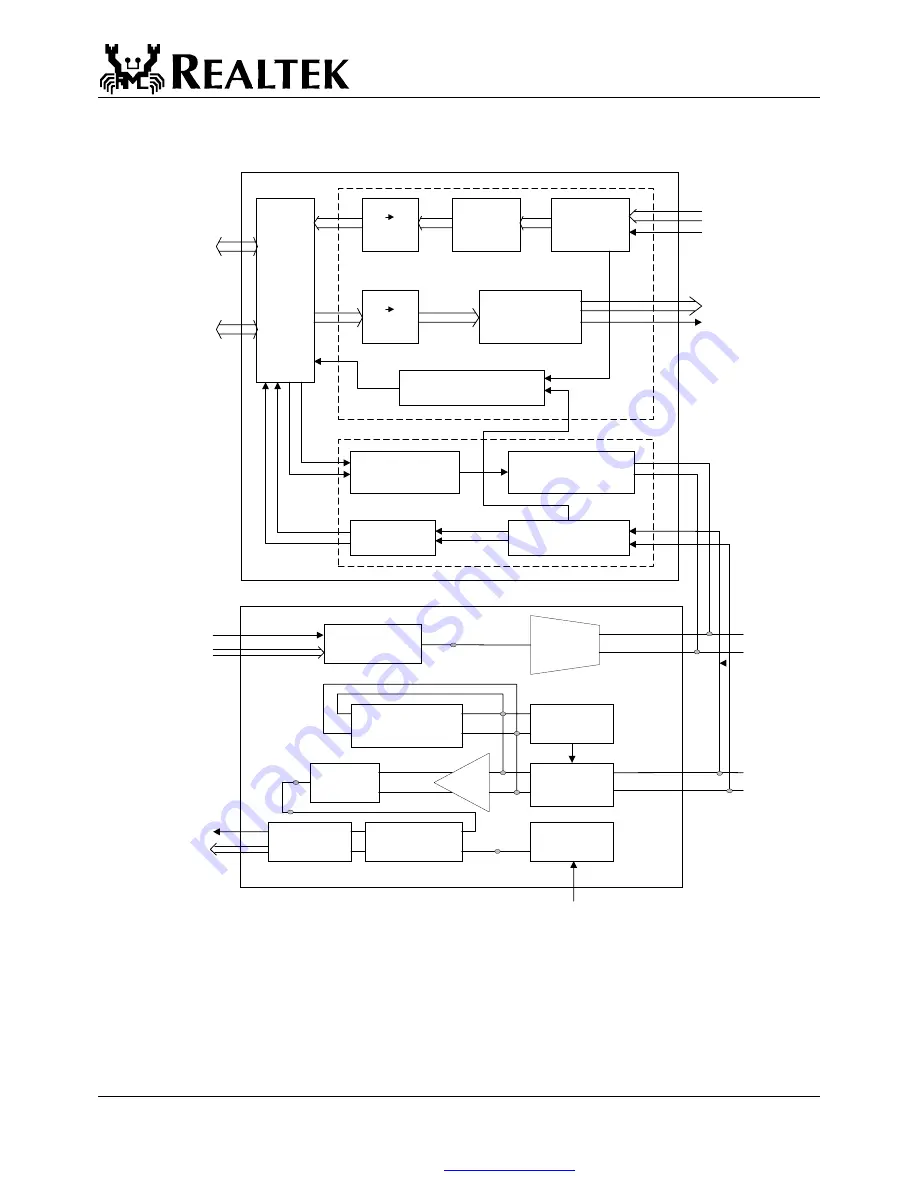

3. Block Diagram

RXIN+

RXIN-

TXO+

TXO -

RXC 25M

25M

TXC 25M

TXD

RXD

TD+

Variable Current

3 Level

Driver

Master

PPL

Adaptive

Equalizer

Peak

Detect

3 Level

Comparator

Control

Voltage

MLT-3

to NRZI

Serial to

Parrallel

ck

data

Slave

PLL

Parrallel

to Serial

Baseline

wander

Correction

5B 4B

Decoder

Data

Alignment

Descrambler

4B 5B

Encoder

Scrambler

10/100

half/full

Switch

Logic

10/100M Auto-negotiation

Control Logic

Manchester coded

waveform

10M Output waveform

shaping

Data Recovery

Receive low pass filter

RXD

RXC 25M

TXD

TXC 25M

TXD10

TXC10

RXD10

RXC10

Link pulse

10M

100M

MII

Interface

SNI

Interface

Tel: +49(0)234-9351135 · Fax: +49(0)234-9351137

E-MAIL:

http://www.

cornelius-consult.de