3DQDVRQLF

22

1.2.3 I

2

C bus

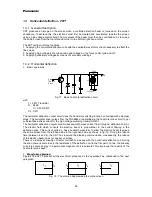

The microcontroller contains an I

2

C bus transceiver hardware interface. The I

2

C bus is a serial

communication system, it requires data line ( SDA ) and associated serial clock line (SCL) ( Philips is

the patent holder of the I

2

C bus standard). Both the SCL and SDA pins are input and open collector

output pins. The I

2

C bus is used by the microcontroller to control the video processor and the non-

volatile memory

Microcontroller

( Master )

TDA8374

( Slave )

5 V

SDA

SCL

EEPROM

( Slave )

Fig : 14 : I

2

C bus devices

1

2

C Bus protocol (SCL and SDA lines)

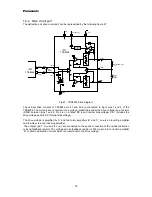

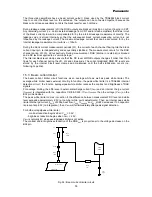

START condition : START is identified by a high to low transition of the SDA line while the clock SCL

is stable in the high state. A START condition must precede any command for data transfer.

STOP condition : STOP is identified by a low to high transition of the SDA line while the clock SCL Is

stable in the high state. A STOP condition terminates communication.

Acknowledge Bit (ACK) : An acknowledge signal is used to indicate a successful data transfer. The

bus transmitter, either master or slave, will release the SDA bus after sending 8 bits of data. During tile

9th clock pulse period the receiver pulls the SDA bus low to acknowledge the receipt of the 8 bits of

data.

SCL

SDA

Start

condition

SDA

input

SDA

change

Stop

condition

SCL

SDA

1

2

3

8

9

MSB

ACK

Fig. 15 : I

2

C protocol

*