52

µ

PD754202, 754202(A)

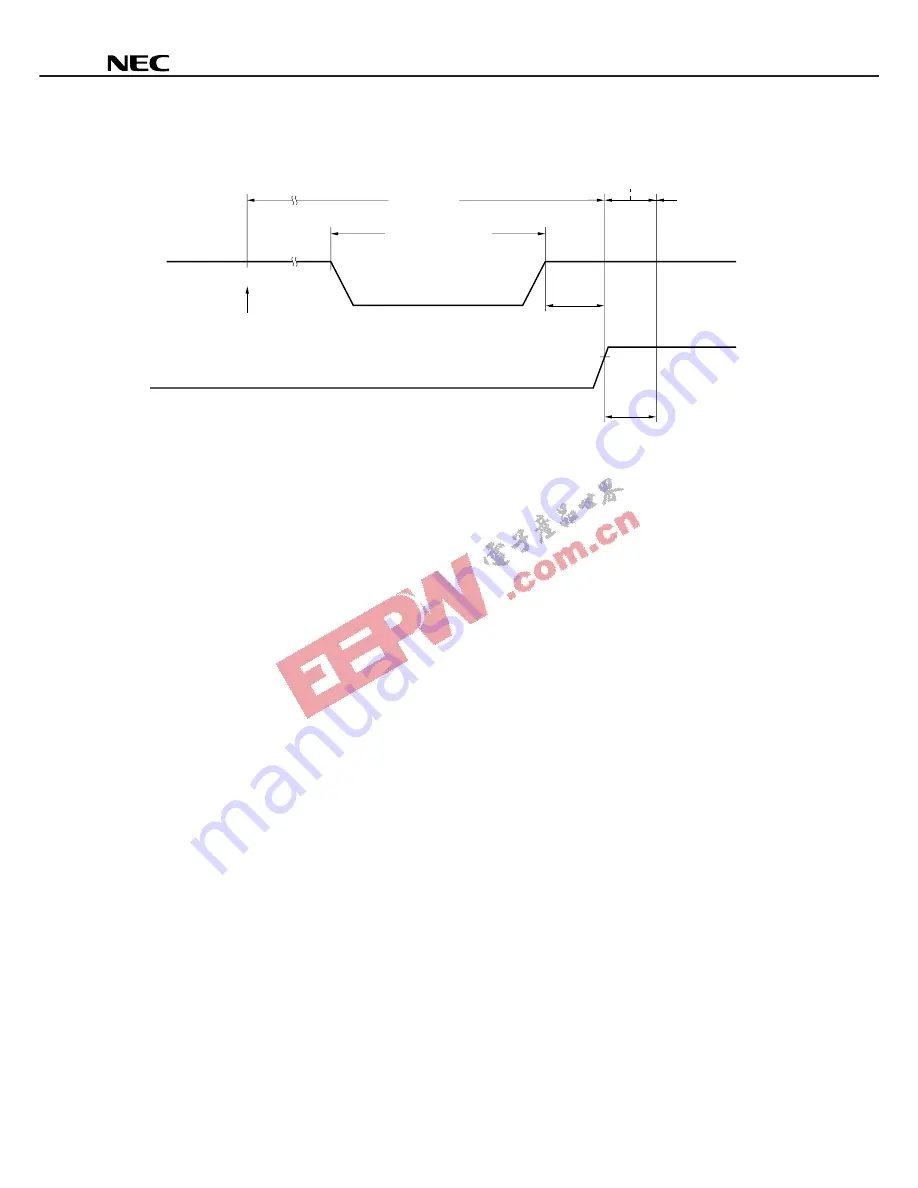

Data Retention Timing (Standby release signal: on releasing STOP mode by interrupt signal)

STOP mode

Data retention mode

Execution of STOP instruction

V

DD

Standby release signal

(interrupt request)

t

WAIT

t

SREL

HALT mode

Operation mode