Nations Technologies Inc.

Tel

:

+86-755-86309900

:

Address: Nations Tower, #109 Baoshen Road, Hi-tech Park North.

Nanshan District, Shenzhen, 518057, P.R.China

304

/

631

through the timeout value.

LPTIM interrupts

The following events generate an interrupt/wake-up event, if they are enabled through the LPTIM_INTEN register:

Compare match

Auto-reload match (whatever the direction if encoder mode)

External trigger event

Autoreload register write completed

Compare register write completed

Direction change (encoder mode), programmable (up / down / both).

Note: If any bit in the LPTIM_INTEN register (Interrupt Enable Register) is set after that its corresponding flag in

the LPTIM_INTSTS register (Status Register) is set, the interrupt is not asserted.

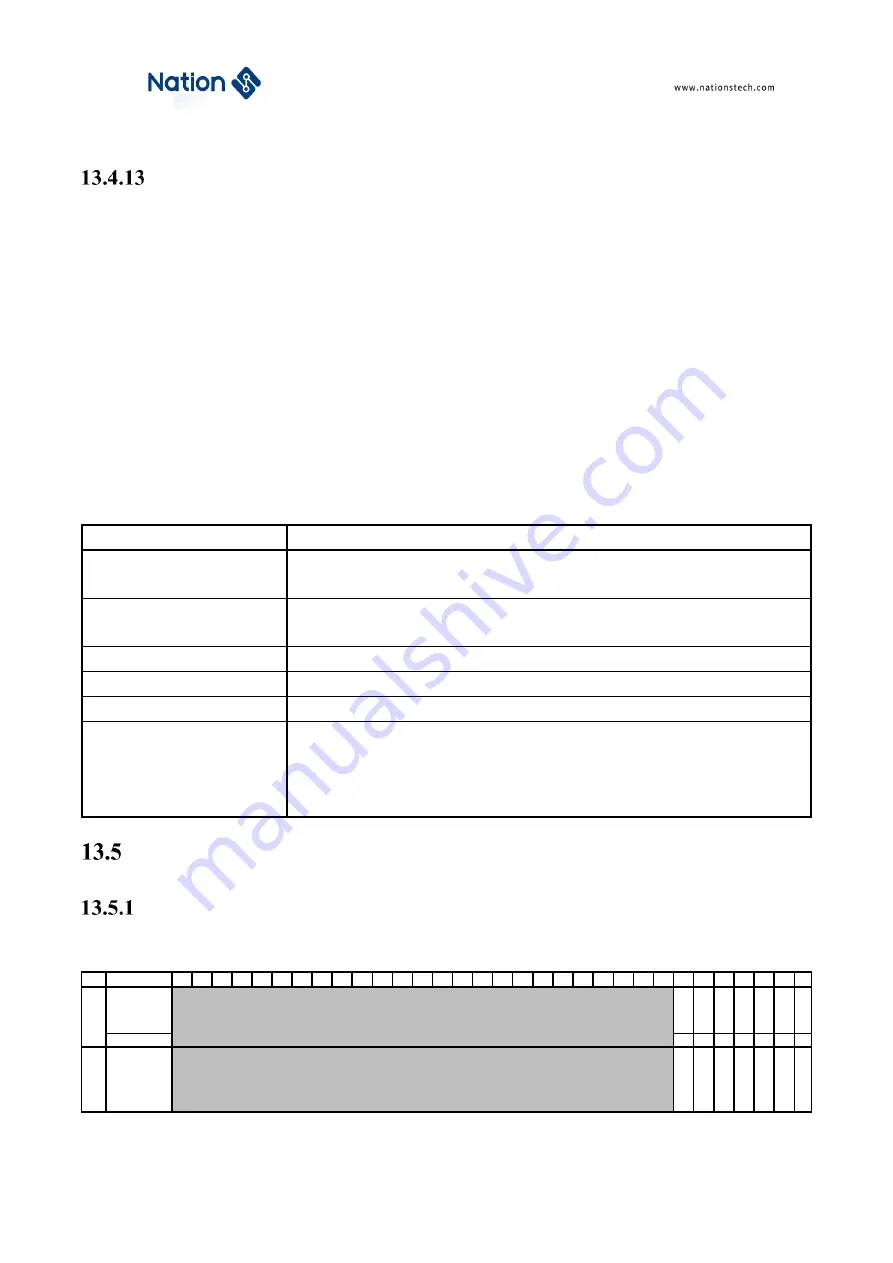

Table 13-4 Interruption events

Corresponding interrupt event

Describe

Compare match

Interrupt flag is set when LPTIM_CNT(counter register value) = LPTIM_COMP(compare

register value).

Auto reload match

Interrupt flag is set when LPTIM_CNT(counter register value) = LPTIM_ARR (auto-reload

register value).

External trigger event

Interrupt flag is set when an external trigger event is detected.

Auto-reload register update OK

Interrupt flag is set when the write operation to the LPTIM_ARR register is complete.

Compare register update OK

Interrupt flag is set when the write operation to the LPTIM_COMP register is complete.

Direction change

Used in Encoder mode. Two interrupt flags are embedded to signal

direction change:

– UP flag indicated that the count direction is changed to count up.

– DOWN flag indicated that the count direction is changed to count down.

LPTIM registers

LPTIM register overview

Table 13-5 LPTIM register overview

Offset

Register

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

000h

LPTIM_INTSTS

Reserved

DO

W

N

UP

AR

R

UPD

C

M

P

UPD

E

XT

R

IG

AR

R

M

C

M

P

M

Reset Value

0

0

0

0

0

0

0

004h LPTIM_INTCLR

Reserved

DO

W

NC

F

UPC

F

AR

R

UPDC

F

C

M

P

UPDC

F

E

XT

R

IGC

F

AR

R

M

C

F

C

M

P

M

C

F