Nations Technologies Inc.

Tel

:

+86-755-86309900

:

Address: Nations Tower, #109 Baoshen Road, Hi-tech Park North.

Nanshan District, Shenzhen, 518057, P.R.China

310

/

631

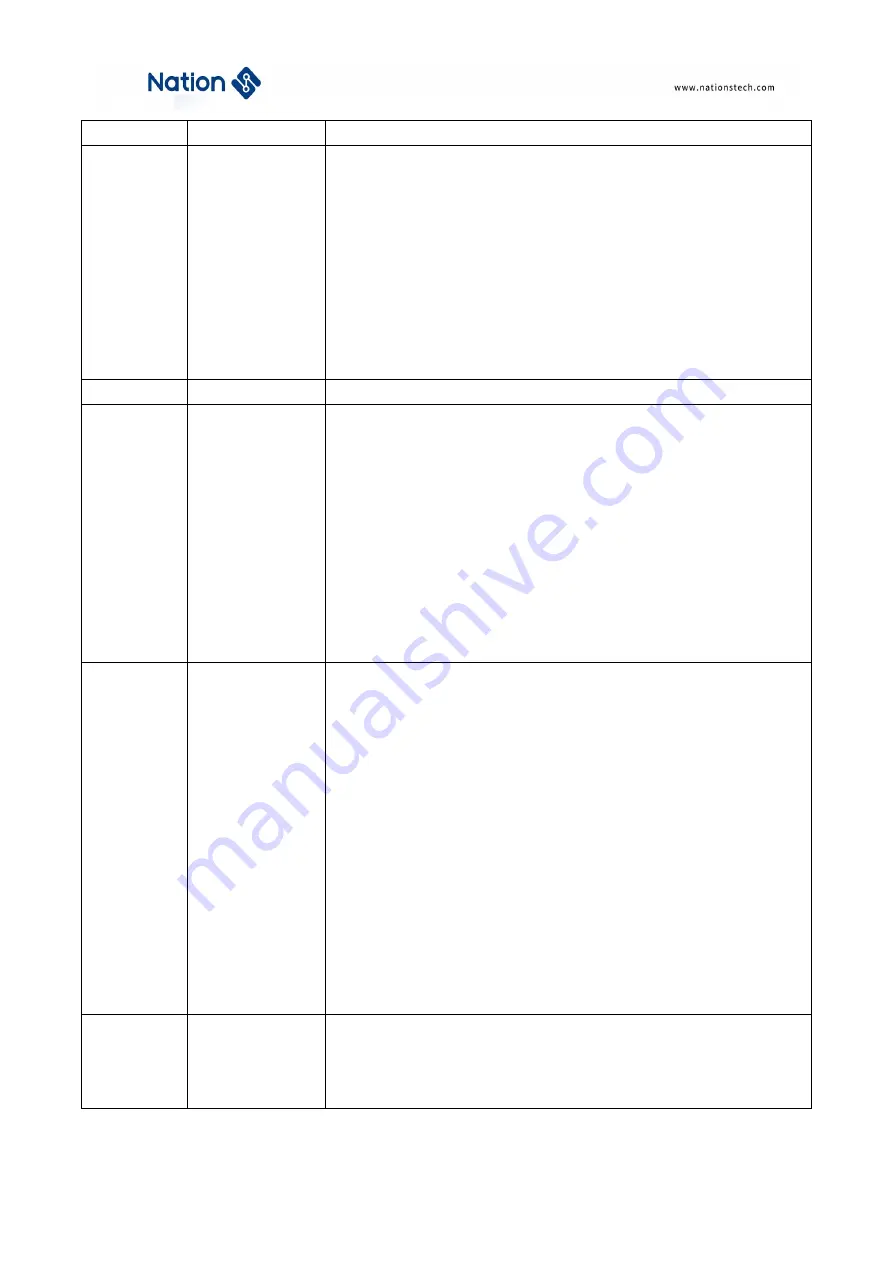

Bit Field

Name

Description

The TRIGFLT value sets the number of consecutive equal samples that should be

detected when a level change occurs on an internal trigger before it is considered as a

valid level transition. An internal clock source must be present to use this feature

00: Any trigger active level change is considered as a valid trigger.

01: Trigger active level change must be stable for at least 2 clock periods before it is

considered as valid trigger.

10: Trigger active level change must be stable for at least 4 clock periods before it is

considered as valid trigger.

11: Trigger active level change must be stable for at least 8 clock periods before it is

considered as valid trigger.

5

Reserved

Reserved, the reset value must be maintained.

4:3

CLKFLT[1:0]

Digital filter external clock input configuration

The CLKFLT value sets the number of consecutive equal samples that should be

detected when a level change occurs on an external clock signal before it is considered

as a valid level transition. An internal clock source must be present to use this feature

00: Any external clock signal level change is considered as a valid transition.

01: External clock signal level change must be stable for at least 2 clock periods

before it is considered as valid transition.

10: External clock signal level change must be stable for at least 4 clock periods

before it is considered as valid transition.

11: External clock signal level change must be stable for at least 8 clock periods

before it is considered as valid transition.

2:1

CLKPOL[1:0]

Clock Polarity

If LPTIM is clocked by an external clock source:

When the LPTIM is clocked by an external clock source, CLKPOL bits is used to

configure the active edge or edges used by the counter:

00: The rising edge is the active edge used for counting

01: The falling edge is the active edge used for counting

10: Both edges are active edges.

11: Not allowed

Note: When both external clock signal edges are considered active ones, the LPTIM

must also be clocked by an internal clock source with a frequency equal to at least

four time the external clock frequency.

If the LPTIM is configured in Encoder mode (LPTIM_CFG.ENC bit is set):

00: The encoder rising edgecounting mode.

01: The encoder falling edge counting mode.

10: The encoder both edges counting mode.

0

CLKSEL

Clock selector

The CKSEL bit selects which clock source the LPTIM will use:

0: LPTIM is clocked by internal clock source (APB1 clock or any of the embedded

oscillators)