2015-2017 Microchip Technology Inc.

DS00001855E-page 37

USB5744

9.7

Clock Specifications

The device can accept either a 25MHz crystal or a 25MHz single-ended clock oscillator (±50ppm) input. If the single-

ended clock oscillator method is implemented,

XTALO

should be left unconnected and

XTALI/CLK_IN

should be

driven with a nominal 0-3.3V clock signal. The input clock duty cycle is 40% minimum, 50% typical and 60% maximum.

It is recommended that a crystal utilizing matching parallel load capacitors be used for the crystal input/output signals

(

XTALI

/

XTALO

). The following circuit design (

) are required to ensure proper

operation.

9.7.1

CRYSTAL SPECIFICATIONS

It is recommended that a crystal utilizing matching parallel load capacitors be used for the crystal input/output signals

(

XTALI

/

XTALO

). Refer to

for the recommended crystal specifications.

Note 6:

Frequency Deviation Over Time is also referred to as Aging.

FIGURE 9-6:

25MHZ CRYSTAL CIRCUIT

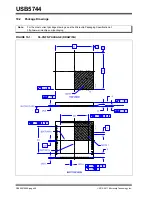

TABLE 9-10:

CRYSTAL SPECIFICATIONS

Parameter

Symbol

Min

Nom

Max

Units

Notes

Crystal Cut

AT, typ

Crystal Oscillation Mode

Fundamental Mode

Crystal Calibration Mode

Parallel Resonant Mode

Frequency

F

fund

-

25.000

-

MHz

Frequency Tolerance @ 25

o

C

F

tol

-

-

±50

PPM

Frequency Stability Over Temp

F

temp

-

-

±50

PPM

Frequency Deviation Over Time

F

age

-

±3 to 5

-

PPM

Total Allowable PPM Budget

-

-

±100

PPM

Shunt Capacitance

C

O

-

7 typ

-

pF

Load Capacitance

C

L

-

20 typ

-

pF

Drive Level

P

W

100

-

-

uW

Equivalent Series Resistance

R

1

-

-

50

Ω

Operating Temperature Range

-

o

C

XTALI/CLK_IN

Pin Capacitance

-

3 typ

-

pF

XTALO

Pin Capacitance

-

3 typ

-

pF

USB5744

XTALO

XTALI

Y1

C

1

C

2