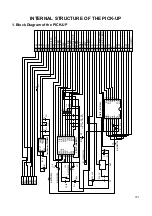

Functional Block Diagram

44

Data

Slicer

Data

PLL

Sync.

Protection

PWM

DAC

RFZC/

TEZC

Circuit

Servo

ADC

RDM &

PWM DAC

ASP

Control

Interface

OPC/ROPC

Computation

Unit

Laser Power

Control

Logic

Time to

Digital

Converter

Audio/Effect

Interface

CDROM

High-speed

Audio Playback

Host

Data

FIFO

ATAPI

Packet

FIFO

3K

SRAM

Key/LED

Interface

Host Interface

8032

Micro-controller

Audio DAC

Audio

Digital Out

Servo

DSP

CLV/CAV

Controller

CIRC/RSPC

Error Corrector

Wobble

Spindle

Control

Wobble Signal

Interface Logic

EFMPLL

(efmclk

synthesizer)

Reset

logic

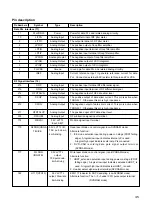

TEST

H11T

SRVSH

WBLSH

RFPDSH

WFPDSH

WLDON

RLDON

ODON

OSCEN

CMOD

CFREQ

WXR

EFMPLLVSS

EFMLPFGND

EFMVCOIN

EFMPLLVDD33

WBLCLK

WBLS1

RFSUB1

RFIP

RFIN

WBLS1

SCOP

RFDTSLVN

RFDTSLVP

PLLVDD33

IREF

LPFIN

LPFIP

PLLVSS

JITFN

LPFON

LPFOP

LPION

LPIOP

JITFO

DMO

FG

TEZISLV

TEI

HRFZC

ADCVDD33

FEI

TEI

CSO

RPLEVEL

ADCVSS

FOO

TRO

FMO

FMO2

PWMOUT

PWM2VREF

PWMVREF

XRST#

XLCK

XLAT#

XDATA

GIO

LO

DACVREF

RO

DACVDD33

DACVSS

ADGO

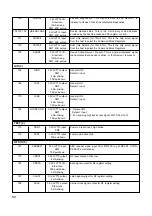

HD[15:0]

PDIAG#

DASP#

HRST#

DIOW#

DIOR#

MACK#

HA[2:0]

CS1FX#

CS3FX#

DMARQ

IORDY

INTRQ

IOCS16#

UPSEN#

UP3_2/UNIT0#

UP3_3/UINT1#

UALE

UP0[7:0]/UAD[7:0]

UP2_7-UP2_0

UP3_5-UP3_4

UP3_1-UP3_0

UP3_6/UWR#

UP3_7/URD#

UA[7:0]

UA16/UP1_0

UA17/UP1_1

UA18/UP1_2

PRST#

XTALO

XTALI

IPLLVDD33

IPLLVSS

RD(15:0)

RA(11:0)

RAS#

CASL#

CASH#/RWEH#

RWE#

ROE#

CLK

CKE

DQML

BA(1:0)

EJECT#/STOP#

PLAY#/PAUSE#

system

clock

System

Clock

Generator

Servo

status

detection

circuit

CIRC Encoder

EFM modulation

Subcode generator

DMU

C3

Encoder

C3

Decoder

CDROM

Sync.

Detection

Descrambler

ATIP Sync Protection &

CRC check &

Target MSF Search

FM Demodulator

& Bi-Phase data

Demodulator

Buffer

Memory

Controller

Write Strategy

Interface Logic

EFM/EFM+

Demodulator

Subcode/ID

Demodjlator