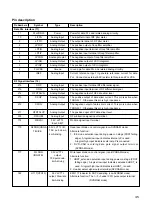

49

EFMPLL VCO (4)

55

EFMPLLVDD33

Analog power(3.3V)

Power supply for EFMPLL circuitry.

54

EFMVCOCIN

Analog input

EFMPLL VCO input. For external loop filter connection.

52

EFMPLLVSS

Ground

Ground pin for EFMPLL circuitry.

53

EFMLPFGND

Analog input

EFMPLL LPF ground input.

Crystal Interface (2)

185

XTALI

Input

X’tal input. The working frequency is 33.88688 MHz.

184

XTALO

Output

X’tal output.

Memory Interface (38)

84

BA1

SDRAM bank address 1 signal. When 4-bank SDRAM is used,

this pin is used to select bank2 and bank3 space and must

connect to “BA1” pin of SDRAM.

When two 2-bank SDRAM are used, this pin is used as “Chip

Select” signal output for second SDRAM and must connect to

“CS#” pin of second SDRAM.

When two DRAM are used, this pin is used as “Row Address

Strobe”, signal output for second DRAM and must connect to

“RAS#” pin of second DRAM.

Default : 4mA, slew rate

85

BA0

SDRAM bank address 0 signal. For SDRAM application only.

Default : 4mA, slew rate

87

ROE#

RAM Output Enable, low active.

For SDRAM application this pin is “Chip Select” signal output

connect to “CS#” pin of SDRAM. When two 2-bank SDRAM are

used, this pin must connect to “CS#” pin of first SDRAM.

Default : 4mA, slew rate.

88

RAS#

RAM Row Address Strobe. This active -low output is the Row

Address Strobe signal to the RAM.

For SDRAM application, this pin is “row address strobe” signal

output connected to SDRAM.

Default : 4mA, slew rate.

90

CASL#

Column Address Strobe Low / Column Address Strobe. When two

column address strobe pins are used, this pin is the Column

Address Strobe Low signal for accessing the lower bytes of a two-

CAS# 16-bit RAM. When an 8-bit DRAM is used, this pin shall be

connected to CAS# of the DRAM.

For SDRAm apllication, this pin is “column address strobe” signal

output connected to SDRAM.

Default : 4mA, slew rate.

91

RWE#

RAM Write Enable/RAM Write Enable Low. RAM write enable

signal, low active. When two write enable pins are used, it is the

Write Enable Low signal for writing the lower bytes of a two-

WE_16-bit RAM.

For SDRAM application, this pin is dedicated for “Write Enable”

usage.

Default : 4mA, slew rate.

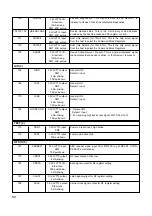

3.3V LVTTL output,

PSR,

2mA, 4mA, 6mA,

8mA, 10mA, 12mA,

14mA, 16mA PDR

3.3V LVTTL I/O,

PSR,

2mA, 4mA, 6mA,

8mA, 10mA, 12mA,

14mA, 16mA PDR

3.3V LVTTL Output,

PSR,

2mA, 4mA, 6mA,

8mA, 10mA, 12mA,

14mA, 16mA PDR

3.3V LVTTL Output,

PSR,

2mA, 4mA, 6mA,

8mA, 10mA, 12mA,

14mA, 16mA PDR

3.3V LVTTL Output,

PSR,

2mA, 4mA, 6mA,

8mA, 10mA, 12mA,

14mA, 16mA PDR

3.3V LVTTL Output,

PSR,

2mA, 4mA, 6mA,

8mA, 10mA, 12mA,

14mA, 16mA PDR