TH-V70

1-34

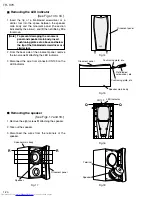

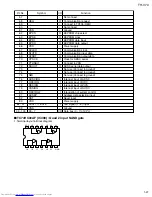

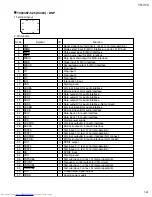

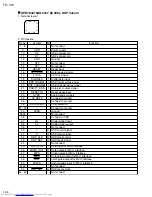

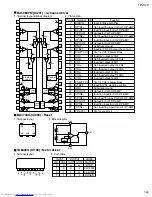

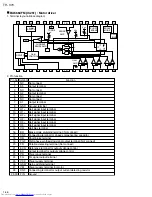

1.Terminal layout

NDV8601VWA-BB (IC501) : DVD on a chip processor

1

60

180

121

240 181

61 120

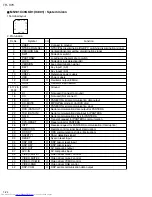

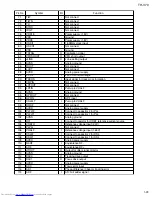

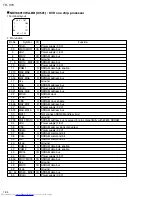

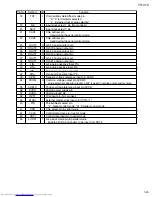

1

2,3

4

5

6

7 - 9

10

11

12,13

14

15,16

17

18

19

20,21

22

23

24

25,26

27

28,29

30

31

32,33

34

35

36

37

38

39

40

41

42

43

44

45,46

47

48

49

50 - 52

53

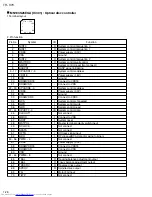

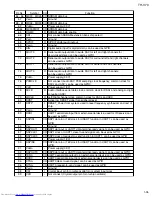

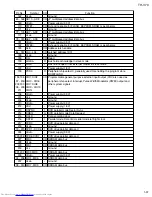

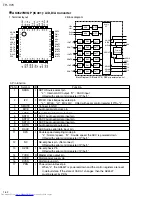

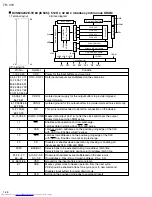

2. Pin function

Vddio

MD10,MD11

Vdd

MD12

Vssio

MD13 - MD15

Vddio

DQM1

MA9,MA8

Vssio

MA7,MA6

Vss

MA5

Vddio

MA4,MA3

MCLK

Vssio

CKE

MA2,MA1

Vddio

MA0,MA10

MA11

Vssio

MA12,MA13

Vdd

CS0-

Vddio

RAS-

CAS-

WE-

Vssio

DQM0

DQM2

MD16

Vddio

MD17,MD18

Vss

MD19

Vssio

MD20 - MD22

Vddio

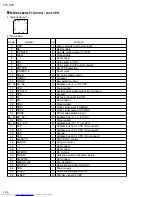

-

I/O

-

I/O

-

I/O

-

O

O

-

O

-

O

-

O

O

-

O

O

-

O

-

-

O

-

O

-

O

O

O

-

O

O

I/O

-

I/O

-

I/O

-

I/O

-

Power supply (3.3V)

SDRAM data bus

Power supply (1.8V)

SDRAM data bus

Ground

SDRAM data bus

Power supply (3.3V)

SDRAM data byte enable

SDRAM address bus

Ground

SDRAM address bus

Ground

SDRAM address bus

Power supply (3.3V)

SDRAM address bus

SDRAM clock

Ground

SDRAM clock enable

SDRAM address bus

Power supply (3.3V)

SDRAM address bus

Not connect (SDRAM address bus)

Ground

SDRAM address bus, reserved for pin compatibility with 63-Mb SDRAM

Power supply (1.8V)

SDRAM primary bank chip select

Power supply (3.3V)

SDRAM command bit

SDRAM command bit

SDRAM command bit

Ground

SDRAM data byte enable

SDRAM data byte enable

SDRAM data bus

Power supply (3.3V)

SDRAM data bus

Ground

SDRAM data bus

Ground

SDRAM data bus

Power supply (3.3V)

Function

I/O

Pin No.

Symbol

Summary of Contents for TH-V70

Page 55: ...TH V70 1 55 M E M O ...