Datasheet

81

Register Description

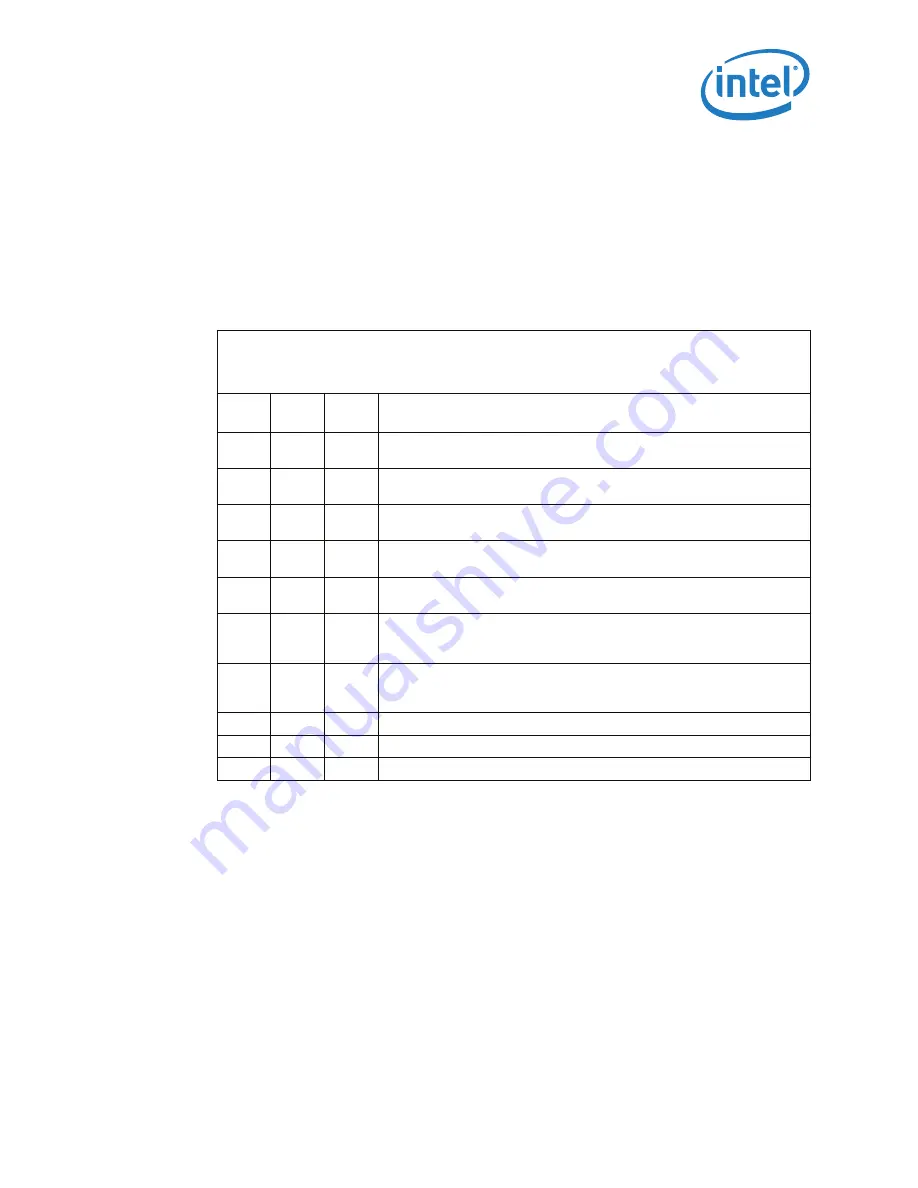

2.10.36 MC_CHANNEL_0_ADDR_MATCH

MC_CHANNEL_1_ADDR_MATCH

MC_CHANNEL_2_ADDR_MATCH

This register specifies the intended address or address range where ECC errors will be

injected. It can be set to match memory address on a per channel basis. The address

fields can be masked in the Mask bits. Any mask bits set to 1 will always match. To

match all addresses, all of the mask bits can be set to 1. The

MC_CHANNEL_X_ECC_ERROR_INJECT register can be used to set the trigger for the

error injection.

Device:

4, 5, 6

Function: 0

Offset:

F0h

Access as a Qword

Bit

Type

Reset

Value

Description

41

RW

0

MASK_DIMM.

1 = If set, ignore DIMM address during address comparison.

40

RW

0

MASK_RANK.

1 = If set, ignore RANK address during address comparison.

39

RW

0

MASK_BANK.

1 = If set, ignore BANK address during address comparison.

38

RW

0

MASK_PAGE.

If set, ignore PAGE address during address comparison.

37

RW

0

MASK_COL.

1 = If set ignore, COLUMN address during address comparison.

36

RW

0

DIMM.

DIMM address for 1 or 2DPC. For 3DPC, bits 36 and 35 represent the DIMM

address and bit 34 represent the RANK address.

35:34

RW

0

RANK.

Rank address for 1 or 2DPC. For 3DPC, bits 36 and 35 represent the DIMM

address and bit 34 represent the RANK address.

33:30

RW

0

BANK. Bank address.

29:14

RW

0

PAGE. Page address.

13:0

RW

0

COLUMN. Column address.

Summary of Contents for I7-900 DEKSTOP SPECIFICATION

Page 10: ...10 Datasheet...

Page 14: ...Introduction 14 Datasheet...