38

Tsi620 Evaluation Board User Manual

60D7000_MA001_03

Intergrated Device Technology

www.idt.com

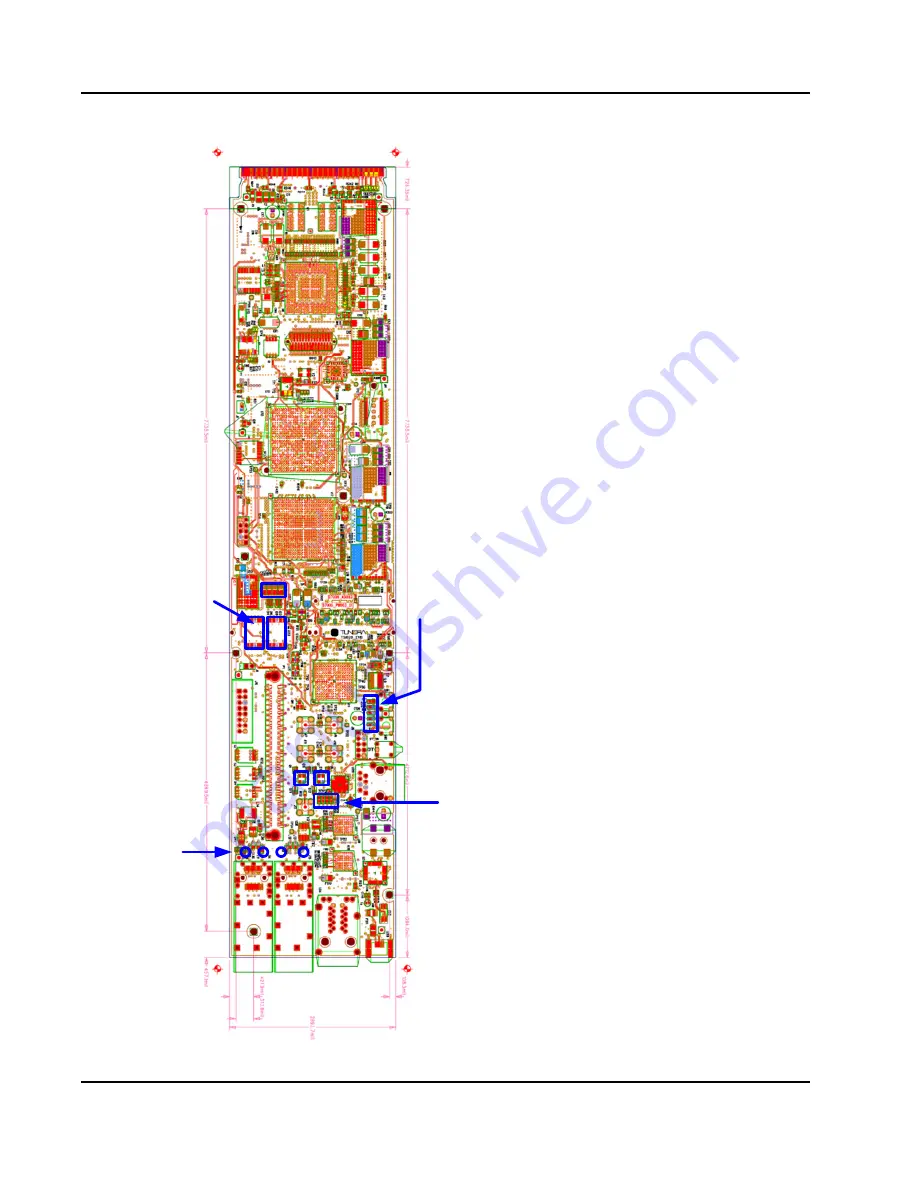

Figure 12: Location of LEDs and Displays (Top View)

J1

4-F

P

G

A

S

F

P

J1

5-D

S

P S

F

P

D21

U2

1

U2

2

2-C

h

ar

s

LE

D Di

sp

la

y

D22

D20

D16

D17

D3

D5

D6

D7

D1

5

D1

4

D1

3

D1

2

D1

9

D1

8

D1

1

D1

0

D9

D8