Rev. 1.71

100

April 11, 2017

Rev. 1.71

101

April 11, 2017

HT66F002/HT66F0025/HT66F003/HT66F004

Cost-Effective A/D Flash MCU with EEPROM

HT66F002/HT66F0025/HT66F003/HT66F004

Cost-Effective A/D Flash MCU with EEPROM

•

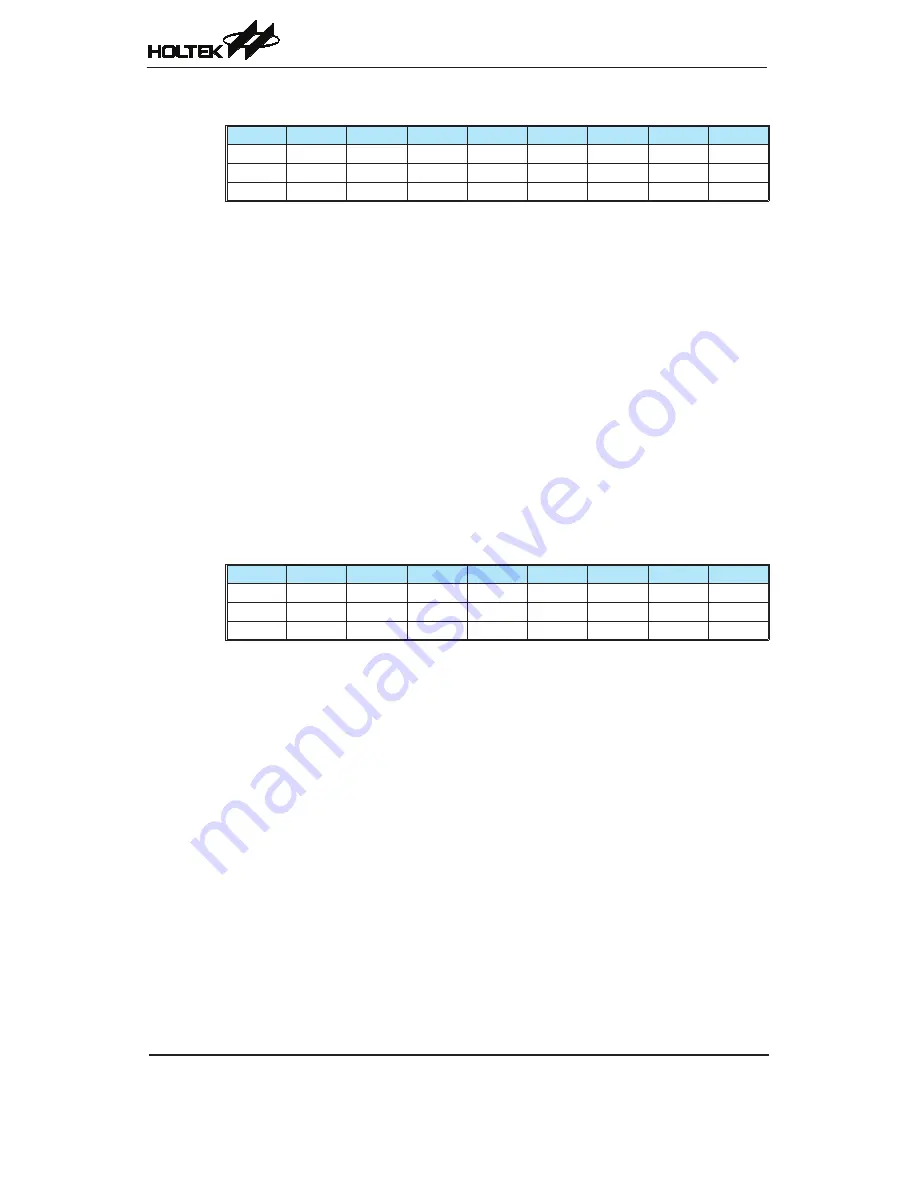

SADC0 Register – HT66F004

Bit

7

6

5

4

3

2

1

0

Name

START

ADBZ

ENADC

ADRFS

—

SACS2

SACS1

SACS0

R/W

R/W

R

R/W

R/W

—

R/W

R/W

R/W

POR

0

0

0

0

—

0

0

0

Bit 7

START

: Start the A/D conversion

0→

1

→0: Start A/D conversion

0→1: Reset the A/D converter and set ADBZ to 0

1

→0: Start A/D conversion and set ADBZ to 1

Bit 6

ADBZ

: ADC busy flag

0: A/D conversion ended or no conversion

1: A/D is busy

Bit 5

ENADC

: ADC enable/disable control register

0: ADC disable

1: ADC enable

Bit 4

ADRFS

: A/D output data format selection bit

0: ADC output data format → SADOH=D[11:4]; SADOL=D[3:0]

1: ADC output data format → SADOH=D[11:8]; SADOL=D[7:0]

Bit 3~2

Unimplemented, read as “0”

Bit 1~0

SACS2~SACS0

: ADC input channels selection

000: ADC input channel comes from AN0

001: ADC input channel comes from AN1

010: ADC input channel comes from AN2

011: ADC input channel comes from AN3

100: ADC input channel comes from AN4

101: ADC input channel comes from AN5

110: ADC input channel comes from AN6

111: ADC input channel comes from AN7

•

SADC1 Register

Bit

7

6

5

4

3

2

1

0

Name

SAINS2

SAINS1

SAINS0

—

—

SACKS2 SACKS1 SACKS0

R/W

R/W

R/W

R/W

—

—

R/W

R/W

R/W

POR

0

0

0

—

—

0

0

0

Bit 7~5

SAINS2~SAINS0

: Internal ADC input channel selection bit

000: ADC input only comes from external pin

001: ADC input also comes from AV

DD

010: ADC input also comes from AV

DD

/2

011: ADC input also comes from AV

DD

/4

101: ADC input also comes from V

R

110: ADC input also comes from V

R

/2

111: ADC input also comes from V

R

/4

Other Values: same as 000

Note: V

R

is OPA output voltage. V

R

can be one of V

REF

/V

REF

×

2/V

REF

×

3/V

REF

×

4/V

BG

×

2/ V

BG

×3/

V

BG

×

4.

Bit 4~3

Unimplemented, read as "0"

Bit 2~0

SACKS2~SACKS0

: ADC clock rate selection bit

000: SACLK=f

SYS

001: SACLK=f

SYS

/2

010: SACLK=f

SYS

/4

011: SACLK=f

SYS

/8

100: SACLK=f

SYS

/16

101: SACLK=f

SYS

/32

110: SACLK=f

SYS

/64

111: SACLK=f

SYS

/128