Rev. 1.20

78

October 28, 2020

BC45B4523

more than 3 bytes, EMD suppression feature will not function because it is treated as normal data frame which is

usually consisted of one data byte and two associated CRC. The EMD suppression is applicable for ISO14443A

protocol, ISO14443B protocol, RxMultiple setting and Receive command. For some reception frame such as

ATQA or part of UID in which response is less than 3 bytes and no error, received data will be passed to FIFO.

Therefore, RxCRCEn shall be set correctly for expected response. When any suppression is detected, EMD_Det

bit (Sector0-0x05.4) is set.

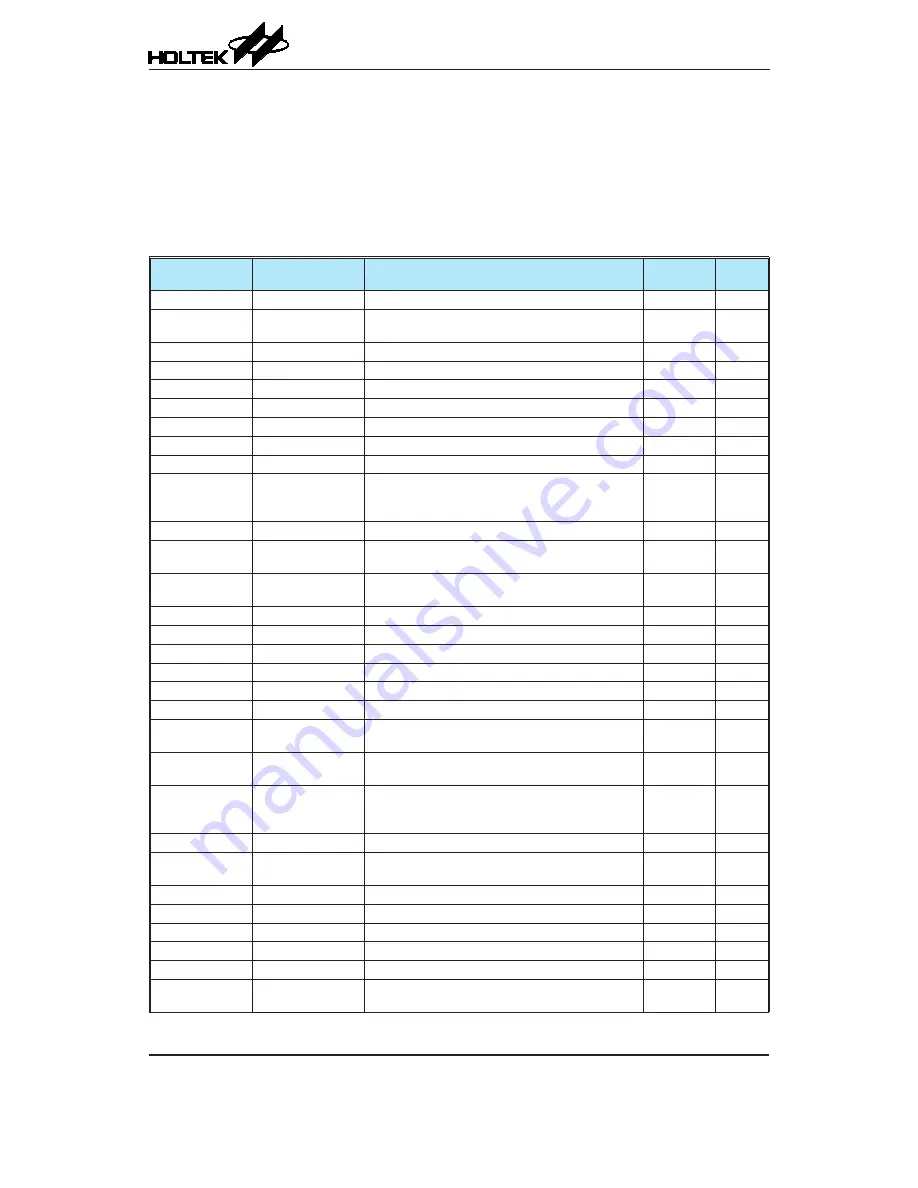

Register Related to Reception

The registers related to reception are summarized in the following table.

Register

Address.Bit

Indication/Usage

Type

Default

Value

Command

Sector0-0x01

Activate Receive or Transceive command

Dynamic

0x00

RxLastBit

Sector0-0x05.[2:0] Displays the number of valid bits in the last

received byte

Read Only

000

RxIEn

Sector0-0x06.3

Configure interrupt enable for RxIRq

Read/Write

0

RxIRq

Sector0-0x07.3

Indicate end of reception

Dynamic

0

CRCErr

Sector0-0x0A.3

Report CRC error in received frame

Read Only

0

FramingErr

Sector0-0x0A.2

Report Framing error in received frame

Read Only

0

ParityErr

Sector0-0x0A.1

Report Parity error in received frame

Read Only

0

CollErr

Sector0-0x0A.0

Report data collision in received frame

Read Only

0

CollPos

Sector0-0x0B

Report collision position in ISO14443A / ISO15693 Read Only

0

RxAlign

Sector0-0x0F.[6:4]

Define the position of the first received data bit

to be stored in the first received byte in the bit

oriented frame in ISO14443A

Dynamic

000

SubCPulses

Sector0-0x19.[7:5]

Define the number of subcarrier pulses per bit

Read/Write

011

SubCCarrier

Sector0-0x19.[4:3]

Define the number of carrier clocks used in

subcarrier

Read/Write

01

LP_Off

Sector0-0x19.2

Switch off all Lowpass filters to extend incoming

signal bandwidth

Read/Write

0

Gain

Sector0-0x19.[1:0]

Define Gain of Amplifier manually

Read/Write

11

RxMultiple

Sector0-0x1A.7

Set to execute consecutive reception

Read/Write

0

CollMaskVal

Sector0-0x1A.6

Setup value of collided bit

Read/Write

0

ZeroAfterColl

Sector0-0x1A.5

Setup value of data after collided bit to be zero

Read/Write

0

RxFraming

Sector0-0x1A.[4:3]

Define decoder framing

Read/Write

01

RxCoding

Sector0-0x1A.[1:0]

Define receiving pattern for decoder

Read/Write

00

BitPhase

Sector0-0x1B

Define the fractional guard time of decoder in unit

of clock

Read/Write

0x3D

MinLevel

Sector0-0x1C.[7:5]

Define the minimum signal strength at the decoder

input that shall be accepted

Read/Write

101

CollLevel

Sector0-0x1C.[3:1]

Define the relative minimum signal strength at the

decoder input that has to be reached by the weaker

half-bit of the Manchester and FSK-coded signal

Read/Write

101

NoRxSOF

Sector0-0x1D.7

Suppress error from SOF-missing frame

Read/Write

0

NoRxEGT

Sector0-0x1D.6

Suppress error from EGT not conforming to the

standard

Read/Write

0

NoRxEOF

Sector0-0x1D.5

Suppress error from EOF-missing frame

Read/Write

0

HP2Off

Sector0-0x1D.4

Switch off the 2

nd

high pass filter

Read/Write

0

TauD

Sector0-0x1D.[3:2]

Defines time constant of internal PLL

Read/Write

01

AGCEn

Sector0-0x1D.1

Enable Automatic gain control

Read/Write

1

TauAGC

Sector0-0x1D.0

Define time constant of AGC

Read/Write

0

Cont_Int

Sector0-0x1E.7

Boost correlator gain by 4x in low data rate of

ISO15693

Read/Write

0