A

A

B

B

C

C

D

D

E

E

4

4

3

3

2

2

1

1

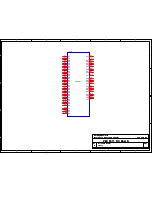

JTAG Port

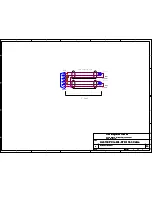

PLL Filter

250mA Max.

Place one cap. to

each edge connector's

3.3V pin.

Place close to the

edge connector

Reset Circuit

PLACE CLOSE TO 8311!

C2 & C3 Are Low ESR Ceramic caps.

NP - provisional

PLACE CLOSE TO 8311!

PLACE CLOSE TO 8311!

CRITICAL PCB LAYOUT, See PLX docs.

PLACE CLOSE TO 8311!

NP

PRSNT

PERp0

PERn0

GPIO0

GPIO2

EERDDATA

ROOT_COMPLEX#

PWR_OK

TCK

GPIO1

LED3

LED4

LED2

LED1

GPIO2

GPIO1

GPIO3

PERST#

PERST_8311#

PERST_8311#

EECS#

BAR0ENB#

EECLK

GPIO3

TMS

TMS

TDO

WAKEIN#

EEWRDATA

TDI

GPIO0

PERST#

WAKEOUT#

BAR0ENB#

ITDO

ITDO

PLXT1

PLXT1

8311_1.5V

8311_3.3V

PCIE3.3VCC

PCIE3.3VCC

PCIE12VCC

8311_PLL1.5VCC

1.5VCC

8311_PLL1.5VCC

PCIE3.3VCC

PCIE12VCC

PCIE3.3VCC

PCIE3.3VCC

PCIE3.3VCC

PCIE12VCC

PCIE3.3VCC

3.3VCC

3.3VCC

1.5VCC

8311_1.5V

8311_3.3V

PCIE3.3VCC

PCIE3.3VCC

PCIE3.3VCC

PCIE3.3VCC

PCIE3.3VCC

8311_1.5V

PCIE12VCC

3.3VCC

PCIE12VCC {5}

Title

Size

Document Number

R e v

Date:

Sheet

o f

A

HI-PCIe_6130, PCIe bus

Holt Integrated Circuits

23351 Madero, Mission Viejo, CA 92691

Custom

2

7

Thursday, September 19, 2013

www.holtic.com

Title

Size

Document Number

R e v

Date:

Sheet

o f

A

HI-PCIe_6130, PCIe bus

Holt Integrated Circuits

23351 Madero, Mission Viejo, CA 92691

Custom

2

7

Thursday, September 19, 2013

www.holtic.com

Title

Size

Document Number

R e v

Date:

Sheet

o f

A

HI-PCIe_6130, PCIe bus

Holt Integrated Circuits

23351 Madero, Mission Viejo, CA 92691

Custom

2

7

Thursday, September 19, 2013

www.holtic.com

R16

1K

LED2

LED

C41

0.1uF

1

2

R29

100

LED4

LED

R19

1K

C10

0.01uF

C18

0.001uF

1

2

R28

0

C29

0.1uF

1

2

LED5

LED

U4

LM1085-3.3, TO-263

VIN

3

GND

1

VOUT

2

C45

0.1uF

1

2

U2

AT25640

SCK

6

CS#

1

SI

5

WP#

3

SO

2

HOLD#

7

GND

4

VCC

8

R22

10k

R26

10K

1

2

C43

0.1uF

1

2

R1

O

R9

0

P1

PCI Express x1 Edge

+12V

B1

+12V

B2

RSVD

B3

GND

B4

SMCLK

B5

SMDAT

B6

GND

B7

+3.3V

B8

JTAG1

B9

3.3Vaux

B10

WAKE#

B11

RSVD

B12

GND

B13

PETp0

B14

PETn0

B15

GND

B16

PRSNT2#

B17

GND

B18

PRSNT1#

A1

+12V

A2

+12V

A3

GND

A4

JTAG2

A5

JTAG3

A6

JTAG4

A7

JTAG5

A8

+3.3V

A9

+3.3V

A10

PERST#

A11

GND

A12

A13

REFCLK-

A14

GND

A15

PERp0

A16

PERn0

A17

GND

A18

C19

0.1uF

1

2

JP3

1

2

3

C38

10uF 10V

J1

1

2

3

4

5

6

C36

0.001uF

1

2

C28

0.1uF

1

2

C27

0.1uF

1

2

R6

1K

R33

1.2K

R23

0_NP

C2

0.1uF

1

2

R31

100

D1

BAT54/SOT

C20

0.001uF

1

2

R30

100

C3

0.1uF

1

2

FB1

1

2

+

C14

47uF 10V

1

2

SW1

SW PUSHBUTTON

R15

1K

R4

10K

1

2

R10

0

+

C11

10uF 16V

R18

1K

R25

NC

C5

1uF 10V

1

2

C34

0.001uF

1

2

R20

1K

C40

0.1uF

1

2

C9

10uF 10V

C39

10uF 10V

C17

0.1uF

1

2

C46

0.1uF

1

2

C33

0.1uF

1

2

JP4

1

2

3

C44

0.1uF

1

2

LED1

LED

C30

0.001uF

1

2

JP2

1

2

3

C32

0.001uF

1

2

C7

0.01uF

1

2

R21

10k

C24

0.001uF

1

2

R11

0

C16

0.1uF

1

2

C21

0.1uF

1

2

C1

0.1uF

1

2

R32

100

TP1

R2

O

R8

1K

C8

0.1uF

JP1

1

2

LED3

LED

C26

0.1uF

1

2

U3

LP2992

VIN

1

VOUT

5

GND

2

BYPASS

4

ON/OFF

3

C22

0.001uF

1

2

C4

0.01uF

C35

0.1uF

1

2

R27

10K

1

2

LED6

LED

C12

.1uF

1

2

+

C25

10uF 16V

1

2

JP5

1

2

3

R5

10K

1

2

U5

MAX6306UK29D3-T

VCC

5

MR#

3

RESET#

1

GND

2

RST_IN

4

PEX83111

U1A

WAKEIN#

B2

ROOT_COMPLEX#

A18

PLXT2

A10

EERDDATA

M3

TEST

N1

BUNRI

F3

BTON

D10

SMC

V4

TMC

E2

TMC1

V3

TMC2

E3

TDI

A14

TCK

A13

TMS

A11

TRST#

B14

WAKEOUT#

D1

PWR_OK

D2

EEWRDATA

L3

EECS#

K3

EECLK

L4

GPIO0

C1

GPIO1

B1

GPIO2

D3

GPIO3

A1

ITDO

C15

BAR0ENB#

E1

H1

REFCLK-

H2

PERp0

G1

PERn0

F2

PERST#

C3

PETp0

J1

PETn0

K2

VSS

A2

VSS

B15

VSS

W3

VSS

W4

VSS

P5

VSS

N5

VSS

M5

VSS

L5

VSS

K5

VSS

J5

VSS

H5

VSS

G5

VSS

M4

VSS

K4

AVSS

J3

VSS_C

F4

VSS_P0

H4

VSS_P1

G4

VSS_R

F1

VSS_RE

G2

VSS_T

K1

VDD3.3

E16

VDD3.3

E17

VDD3.3

F16

VDD3.3

F17

VDD3.3

D8

VDD3.3

D9

VDD3.3

E9

VDD3.3

E15

VDD3.3

F15

VDD3.3

G1

5

VDD1.5

C9

VDD1.5

C13

VDD1.5

D6

VDD1.5

L1

VDD1.5

L2

VDD1.5

M1

VDD1.5

W5

AVDD

G3

VDD_P

J2

VDD_R

H3

VDD_T

J4

VDD1.5

C2

VDD3.3

D7

VDD3.3

E5

VDD3.3

F5

VSS

F11

VSS

F10

VSS

F9

VSS

F8

VSS

F7

PLXT1

A3

TDO

C14

PERR#

T4

R17

1K

R12

10K

R3

1K

C42

0.1uF

1

2

C13

.01uF

1

2

C37

10uF 10V

C23

0.1uF

1

2

RN1

274

1

2

3

4

5

6

7

8

+

C47

47uF 10V

1

2

C31

0.1uF

1

2

R34

330

C6

10uF 10V

TP32

C15 1uF 10V

1

2

R24

0