I OUTLINE: BLOCK DIAGRAM

S1C33210 FUNCTION PART

EPSON

B-I-2-1

I-2 BLOCK DIAGRAM

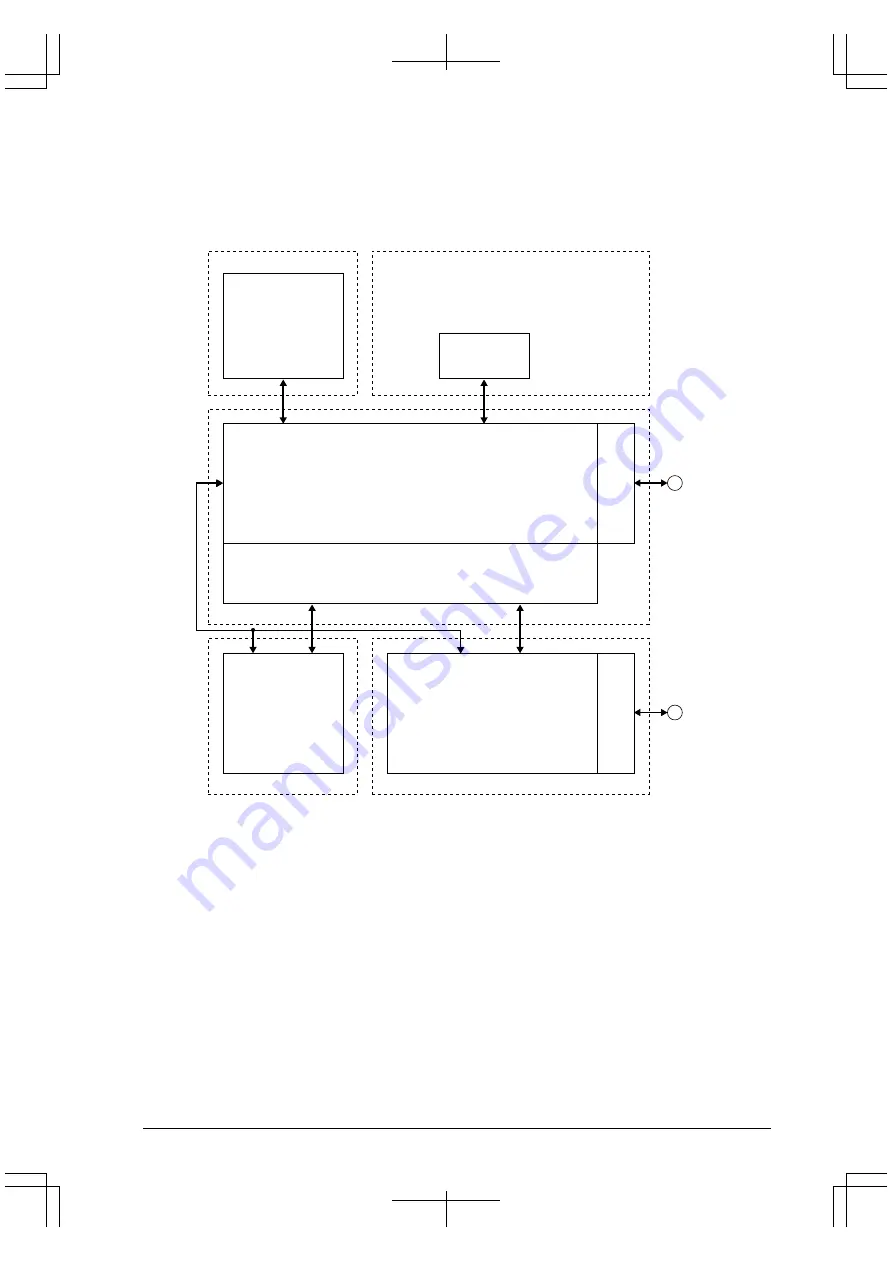

The S1C33210 consists of five major blocks: C33 Core Block, C33 Peripheral Block, C33 Analog Block, C33

DMA Block and C33 Internal Memory Block.

Figure 2.1 shows the configuration of the S1C33 blocks.

CORE_PAD

Pads

C33_SBUS

Internal RAM

(Area 0)

C33 Core Block

C33 Internal Memory Block

C33 DMA Block

PERI_PAD

Pads

C33_PERI

(Prescaler, 8-bit timer, 16-bit timer,

Clock timer, Serial interface,

Mobile access interface, Ports)

C33 Peripheral Block

C33 Analog Block

C33_CORE

(CPU, BCU, ITC, CLG, DBG)

C33_ADC

(A/D converter)

C33_DMA

(IDMA, HSDMA)

Figure 2.1 Block Configuration

Summary of Contents for S1C33210

Page 4: ......

Page 13: ...S1C33210 PRODUCT PART ...

Page 14: ......

Page 124: ...APPENDIX B PIN CHARACTERISTICS A 110 EPSON S1C33210 PRODUCT PART THIS PAGE IS BLANK ...

Page 125: ...S1C33210 FUNCTION PART ...

Page 126: ......

Page 127: ...S1C33210 FUNCTION PART I OUTLINE ...

Page 128: ......

Page 130: ...I OUTLINE INTRODUCTION B I 1 2 EPSON S1C33210 FUNCTION PART THIS PAGE IS BLANK ...

Page 138: ...I OUTLINE LIST OF PINS B I 3 6 EPSON S1C33210 FUNCTION PART THIS PAGE IS BLANK ...

Page 139: ...S1C33210 FUNCTION PART II CORE BLOCK ...

Page 140: ......

Page 142: ...II CORE BLOCK INTRODUCTION B II 1 2 EPSON S1C33210 FUNCTION PART THIS PAGE IS BLANK ...

Page 148: ...II CORE BLOCK CPU AND OPERATING MODE B II 2 6 EPSON S1C33210 FUNCTION PART THIS PAGE IS BLANK ...

Page 152: ...II CORE BLOCK INITIAL RESET B II 3 4 EPSON S1C33210 FUNCTION PART THIS PAGE IS BLANK ...

Page 234: ...II CORE BLOCK CLG Clock Generator B II 6 10 EPSON S1C33210 FUNCTION PART THIS PAGE IS BLANK ...

Page 236: ...II CORE BLOCK DBG Debug Unit B II 7 2 EPSON S1C33210 FUNCTION PART THIS PAGE IS BLANK ...

Page 237: ...S1C33210 FUNCTION PART III PERIPHERAL BLOCK ...

Page 238: ......

Page 240: ...III PERIPHERAL BLOCK INTRODUCTION B III 1 2 EPSON S1C33210 FUNCTION PART THIS PAGE IS BLANK ...

Page 296: ...III PERIPHERAL BLOCK WATCHDOG TIMER B III 5 4 EPSON S1C33210 FUNCTION PART THIS PAGE IS BLANK ...

Page 429: ...S1C33210 FUNCTION PART IV ANALOG BLOCK ...

Page 430: ......

Page 432: ...IV ANALOG BLOCK INTRODUCTION B IV 1 2 EPSON S1C33210 FUNCTION PART THIS PAGE IS BLANK ...

Page 448: ...IV ANALOG BLOCK A D CONVERTER B IV 2 16 EPSON S1C33210 FUNCTION PART THIS PAGE IS BLANK ...

Page 449: ...S1C33210 FUNCTION PART V DMA BLOCK ...

Page 450: ......

Page 452: ...V DMA BLOCK INTRODUCTION B V 1 2 EPSON S1C33210 FUNCTION PART THIS PAGE IS BLANK ...

Page 506: ...V DMA BLOCK IDMA Intelligent DMA B V 3 18 EPSON S1C33210 FUNCTION PART THIS PAGE IS BLANK ...

Page 507: ...S1C33210 FUNCTION PART Appendix I O MAP ...

Page 508: ......

Page 557: ......