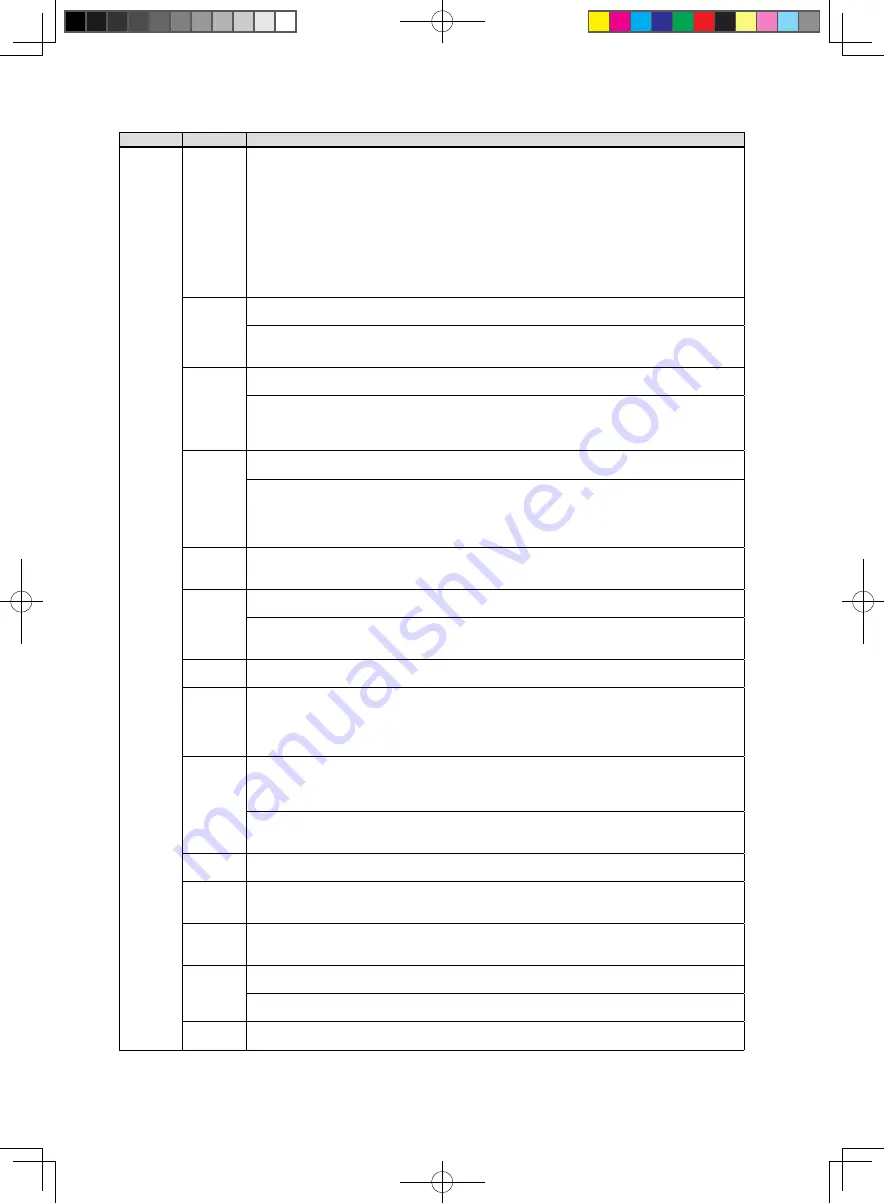

ReViSiOn hiSTORY

Code no.

Page

Contents

411914901

18-4, 18-5 UART: Data reception control

(Old) (2) RDRY = 1, RD2B = 0

... This clears the data inside the buffer and resets the RDRY flag. ...

(3) RDRY = 1, RD2B = 1

... The receive data buffer ... and resetting the RD2B flag. ...

Even when the receive data buffer is full, ... and the new data will overwrite the shift register data.

(New) (2) RDRY = 1, RD2B = 0

... This resets the RDRY flag. ...

(3) RDRY = 1, RD2B = 1

... The receive data buffer outputs the oldest data first. This resets the RD2B flag. ...

Even when the receive data buffer is full, ... In this case, the last received data cannot be read.

19-2

SPI: SPI clock

Modified Figure 19.3.1

SPI: SPI clock

(Old) In slave mode, the SPI clock is input ... differentiated and used to sync with the PCLK clock.

(New) In slave mode, the SPI clock is input via the SPICLK

x

pin.

19-4

SPI: Data transmission timing chart

Deleted Figure 19.5.1

SPI: Data transmission control

(Old) No description

(New) Note: When the SPI module is used in master mode with CPHA set to 0, ... (Added Figure 19.5.1)

... transmit data bits and the second and following bytes during continuous transfer.

19-5

SPI: Data transmission/receiving timing chart

Modified Figure 19.5.2

SPI: Disabling data transfers

(Old) After a data transfer is completed ... the SPRBF flag is 0 before disabling data transfer.

Setting SPEN to 0 empties ... if SPEN is set to 0 while data is being sent or received.

(New) After a data transfer is completed ... the SPBSY flag is 0 before disabling data transfer.

The data being transferred cannot be ... if SPEN is set to 0 while data is being sent or received.

19-7

SPI: SPI Ch.

x

Transmit Data Register (SPI_TXD

x

)

(Old) No description

(New) Note: Make sure that SPEN is set to 1 before writing data ... to start data transmission/reception.

20-2

I2CM: I

2

C connection example

Added Figure 20.2.1

I2CM: Synchronization clock (upper limit of transfer rate)

(Old) No description

(New) When the I2CM module is used to ... 50 kbps in standard mode or 200 kbps in fast mode.

20-3

I2CM: Transmit data specifying slave address and transfer direction

Modified Figure 20.5.2

20-4

I2CM: Data reception control

(Old) The data is loaded to the shift register in sequence at the clock rising edge, with the MSB leading.

RXE is reset to 0 when D6 is loaded.

(New) The data is shifted into the shift register from the MSB first in sync with the clock.

RXE is reset to 0 when D7 is loaded.

20-5

I2CM: End of data transfers (Generating stop condition)

(Old) The stop condition generation can be reserved. ... data transfer (including ACK transfer) ends.

(New) Before STP can be set to 1, confirm that TBUSY or RBUSY is reset to 0 from 1 (this indicates that ...

has finished and the time for the slave device to finish clock stretching has elapsed.

I2CM: Disabling data transfer

(Old) After data transfer has completed ... if I2CMEN is set to 0 during the transfer.

(New) After the stop condition has been generated, ... transfer data at that point cannot be guaranteed.

20-5, 20-6 I2CM: Timing chart

Modified Figures 20.5.6 to 20.5.9

20-8

I2CM: I

2

C Master Control Register (I2CM_CTL) - (D1) STP: Stop Control Bit

(Old) STP is disabled if any of TXE, RXE, or STRT is 1.

(New) Deleted

20-9

I2CM: I

2

C Master Data Register (I2CM_DAT) - (D10) RXE: Receive Execution Bit

(Old) RXE is reset to 0 as soon as D6 is loaded to the shift register.

(New) RXE is reset to 0 as soon as D7 is loaded to the shift register.

21-1

I2CS: I2CS Module overview

Modified Figure 21.1.1

I2CS: List of I2CS Pins - SCL1

Modified Table 21.2.1

21-2

I2CS: I

2

C connection example

Added Figure 21.2.1