CY4636 WirelessUSB™ LP Keyboard Mouse Reference Design Kit User Guide, Doc. # 001-70355 Rev. *A

75

Code Examples

Packet Format 2.

When there is either z-wheel data or button data, the transmitted packet is three

bytes. In the case where there is no X, Y delta data, but there is z-wheel or button data, the X, Y

delta bytes will be set to zero. The z-wheel data is a signed value with bit 4 as the sign bit.

Packet Format 3.

When battery voltage level is communicated, the transmitted packet is 1 byte.

5.2.3.6

Interrupt Usage and Timing

In the RDK mouse, the following interrupts are enabled:

■

Motion interrupt from the optical sensor

■

Button (left, middle, and right buttons) interrupt

■

Bind button interrupt

The ISR module provides an interface to enable/disable individual GPIO interrupts. It also provides

the top level GPIO interrupt handler for the application. The other modules handle User Module spe-

cific interrupts.

The top level handler isr_gpio() calls a routine in the GPIO interrupt User Module. The parameter

passed is a pointer to another C function that has been declared as an interrupt handler. This is done

in order to preserve the registers used in the handler. The gpio_isr_redirector() function manipulates

the stack, preparing it for the interrupt handler being called. The rule is that the module routine being

called may not call any other functions and it must be declared with the #pragma interrupt_handler.

For example, the interrupt handler in the optical module that handles detection of optical motion

does not call any other C functions. Instead, it uses a macro provided by the mouse module to post

an event flag. See the optical/mouse modules. This method prevents the compiler from pushing all

of its virtual registers onto the stack when a function is called at interrupt context.

The interrupt latency includes two portions. The first portion is the time between the assertion of an

enabled interrupt and the start of its ISR, which can be calculated using the following equation:

Latency1 = Time for current instruction to Time for M8C to change program counter to inter-

rupt a Time for LJMP instruction in interrupt table to execute.

For example, if the 5-cycle JMP instruction is executing when an interrupt becomes active, the total

number of CPU clock cycles before the ISR begins would be as follows:

(1 to 5 cycles for JMP to finish) + (13 cycles for interrupt routine) + (7 cycles for LJMP) = 21 to 25

cycles.

In the example above, at 12 MHz, 25 clock cycles take 2.083 µs.

The second portion is the time between the start of the ISR and the post of the event flag. For exam-

ple, the motion interrupt takes 308 CPU clock cycles for this portion. Therefore, the Latency2 equals

to 25.667 µs for the 12 MHz CPU.

Consequently, the total latency for a motion interrupt is:

La Latency2 = 27.750 µs

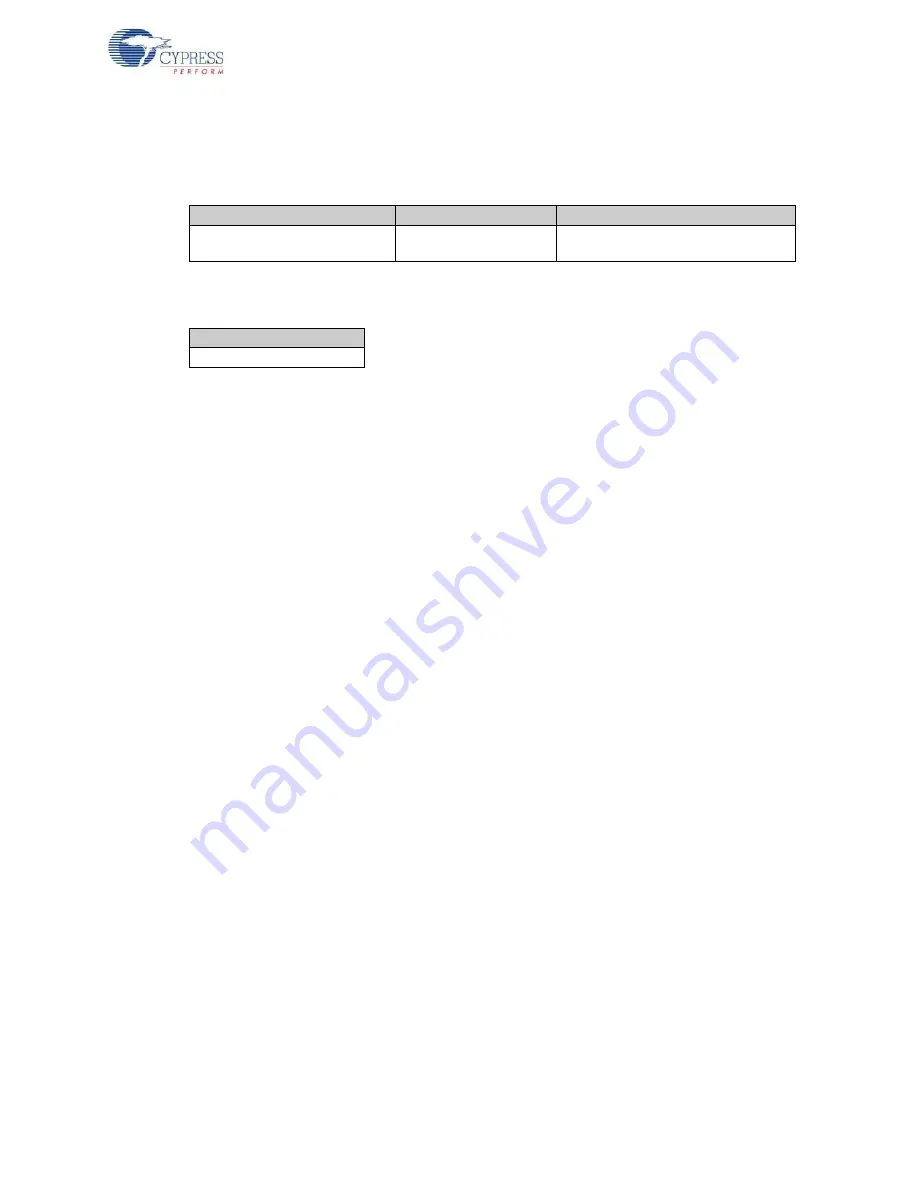

Table 5-9. Packet Format 2

Byte 1

Byte 2

Byte 3

X Delta (8 bits)

Y Delta (8 bits)

Button (Bits[7:5]),

Z Delta (Bits[4:0])

Table 5-10. Packet Format 3

Byte 1

Battery Level (1 - 10)