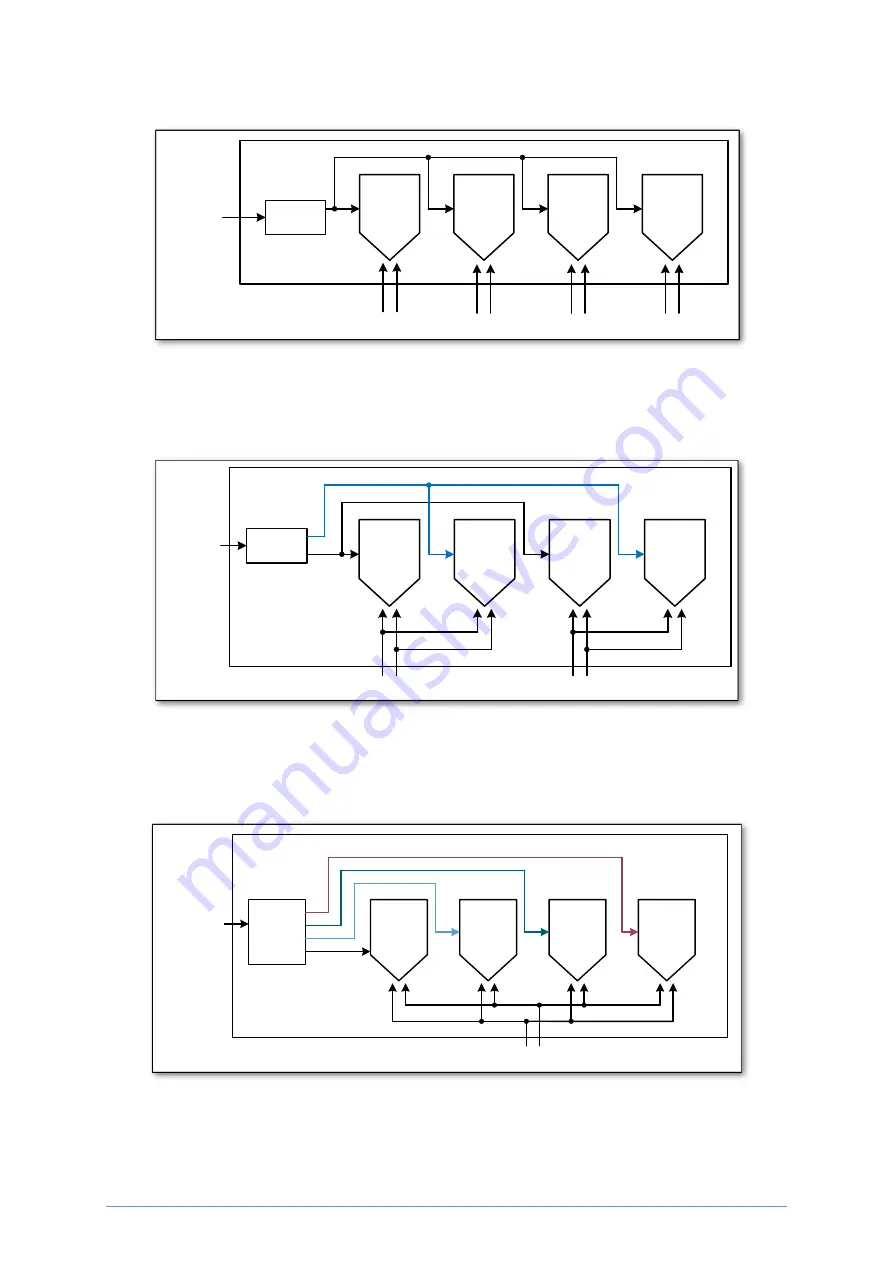

CLK

(2.5 GHz)

Clock

circuit

1.25 GHz

ADC A

1.25 Gsps

ADC B

1.25 Gsps

ADC C

1.25 Gsps

ADC D

1.25 Gsps

AAI, AAIN

BAI, BAIN

CAI, CAIN

DAI, DAIN

Figure 2.7: ADCs in 4 channel mode ABCD at 1.25Gsps.

CLK

(2.5 GHz)

Clock,

circuit

Inverted

1.25 GHz

ADC,A

1.25 Gsps

ADC,B

1.25 Gsps

ADC,C

1.25 Gsps

ADC,D

1.25 Gsps

AAI,,AAIN

DAI,,DAIN

In-phase

1.25 GHz

Figure 2.8: ADCs in 2 channel mode AD, interleaved for 2.5Gsps.

CLK

72.5 GHz)

Clock,

circuit

Inverted

1.25 GHz

ADC,A

1.25 Gsps

ADC,B

1.25 Gsps

ADC,C

1.25 Gsps

ADC,D

1.25 Gsps

AAI,,AAIN,or,BAI,BAIN,or,CAI ,,CAIN,or,DAI ,,DAIN

In-phase

1.25 GHz

90

0

phase

-

shifted

1.25 GHz

270

0

phase -shifted

1.25 GHz

Figure 2.9: ADCs in 1 channel mode A, B, C or D interleaved for 5Gsps.

cronologic GmbH & Co. KG

9

Ndigo5G User Guide

Summary of Contents for Ndigo5G-10

Page 2: ......

Page 3: ......

Page 7: ......

Page 45: ...cronologic GmbH Co KG 40 Ndigo5G User Guide...

Page 54: ...on page 47 cronologic GmbH Co KG 49 Ndigo5G User Guide...