Cyclone 10 LP RefKit User Guide

www.arrow.com

Page | 22

February 2022

Board

Reference

FPGA Pin

No.

Arduino

Header

Pin

Func.

Description

I/O Std

D14_SDA

PIN_E1

J1 / 9

Bidir

Digital I/O [14] or Serial Data Line

3.3 V

D15_SCL

PIN_H3

J1 / 10

Bidir

Digital I/O [15] or Serial Clock Line

3.3 V

n.c.

-

J3 / 1

-

Not connected

-

3.3V

-

J3 / 2

PWR

3.3V power to the connector

-

EXT_RST

PIN_P7

J3 / 3

Bidir

Reset signal of the FPGA

3.3 V

3.3V

-

J3 / 4

PWR

3.3V power to the connector

-

5V

-

J3 / 5

PWR

5V power to the connector

-

GND

-

J3 / 6

PWR

Ground output to the connector

-

GND

-

J3 / 7

PWR

Ground output to the connector

-

n.c.

-

J3 / 8

-

Not connected

-

AIN0

PIN_J6

J4 / 1

Bidir

GPIO [0]

3.3 V

AIN1

PIN_H1

J4 / 2

Bidir

GPIO [1]

3.3 V

AIN2

PIN_J2

J4 / 3

Bidir

GPIO [2]

3.3 V

AIN3

PIN_J1

J4 / 4

Bidir

GPIO [3]

3.3 V

AIN4

PIN_J3

J4 / 5

Bidir

GPIO [4]

3.3 V

AIN5

PIN_J5

J4 / 6

Bidir

GPIO [5]

3.3 V

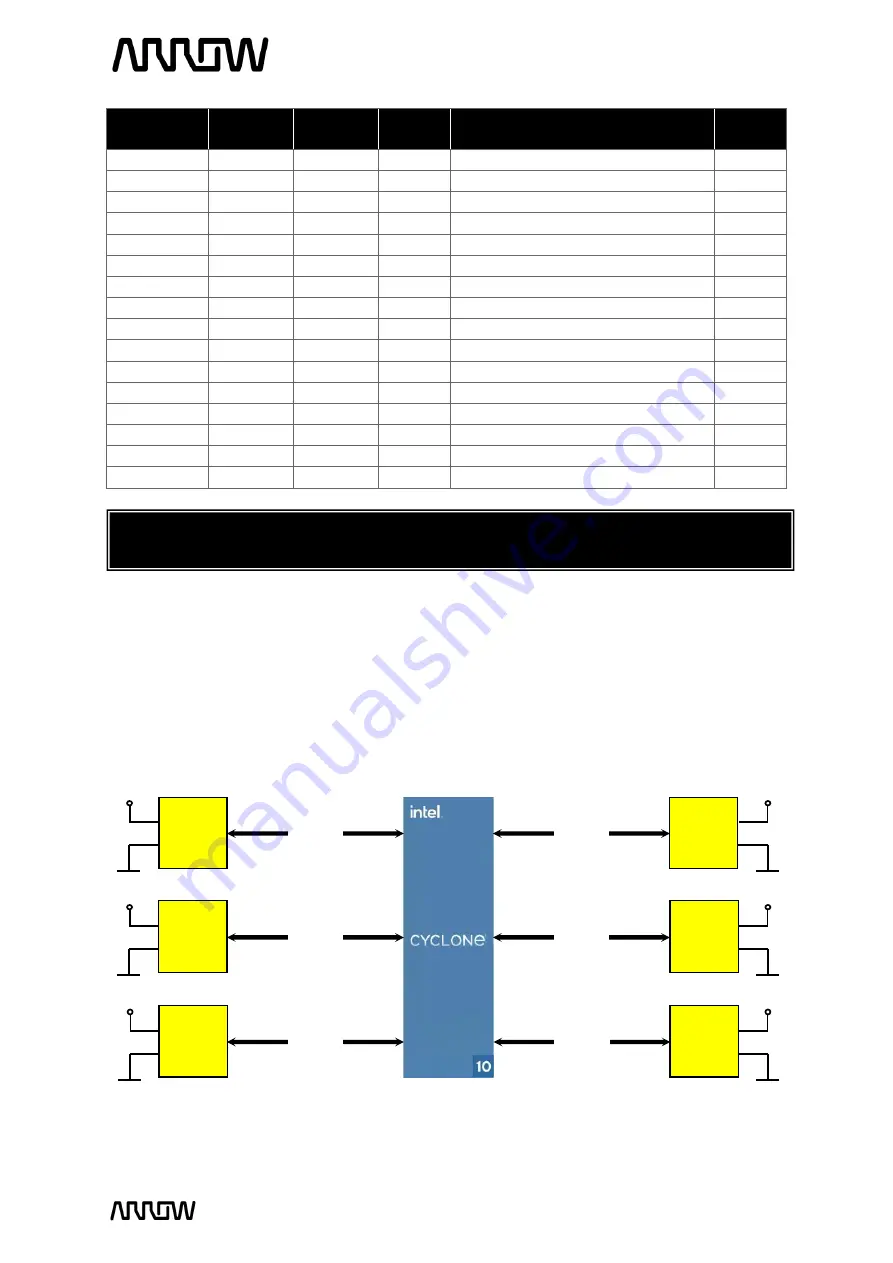

3.3.11

PMOD Connectors

The C10LP RefKit board offers connectivity to PMOD compatible connectors, making it possible

to add a big variety of sensors or ICs to the system. The board has 6 PMOD connectors that can

be configured to 2

6 pins or 1

12 pins

D

c et

D

I

D

c et

D

I

D

c et

D

I

D

c et

D

I

D

c et

D

I

D

c et

D

I

Note: The ADC/DAC is also directly connected to the J4 connector. If AIN5..0 are used as

digital I/Os of the FPGA, make sure that the ADC/DAC does not drive these wires!

Figure 17

–

PMOD Headers Connections