UG-1882

Rev. 0 | Page 7 of 28

REFERENCE

The EVAL-AD4696FMCZ includes an on-board precision

voltage reference and a reference buffer that supplies the REF pin

on the

. The 5 V reference is provided by the

(U3), which is an ultralow noise, high accuracy reference

source. The

(A10) functions as a reference buffer.

C1 functions as the REF decoupling capacitor (see Figure 24).

The EVAL-AD4696FMCZ provides several options for driving the

AD4696 REF input. Jumper JP11 (see Figure 28 and Table 5) selects

between the on-board voltage reference (U3, see Figure 25) and

an external, user supplied reference source (via the P5 terminal

block, see Figure 28).

The selected reference source (on board or external) is also used

to generate a dedicated V

REF

/2 voltage and drive the dc bias

amplifiers, U7 and U9. The dedicated V

REF

/2 voltage is reserved

for setting the COM pin for the COM referenced pseudobipolar

mode. See the Configuring DC Channels (IN2 Through IN15)

section and the Hardware Configurations for Supporting

AD4696 Polarity Modes section for a description of how these

voltages are used in evaluating AD4696 performance.

The AD4696 reference input high-Z mode feature effectively lowers

the current consumption of the REF pin when performing

conversions (see the AD4696 data sheet for more information).

The reference input high-Z mode is enabled by default, but can

be disabled via the REFHIZ_EN bit (see the Memory Map View

section).

Table 5. JP11 Positions for Selecting Reference Source

Position

Reference Source

A

External reference via P5

B (Default)

On-board reference via U3

POWER SUPPLIES

The EVAL-AD4696FMCZ is designed to operate from a 12 V

supply (labeled VPWR_12V) and a 3.3 V supply (labeled

VCC_HOST) provided from the host controller board via the

FMC connector (P1). Alternatively, VPWR_12V can be

provided from an external source via the VPWR test point. If

the controller board in use does not provide the 12 V supply,

the user can provide it through VPWR test point. The on-board

power circuitry converts the 12 V VPWR_12V supply into

voltage rails to power the AD4696, the A0 to A8 amplifiers, the

5 V on-board reference, and other support circuitry.

The

(U2) converts VPWR_12V (12 V) to approximately

7.5 V.

(U4) converts VCC_HOST (3.3 V) to −V_SUP

(−3.3 V). Using 7.5 V and −3.3 V (V_SUP),

(U5)

gen5 V and −2.5 V.

(U6) generates a 1.8 V rail

from the 5 V rail.

Setting Amplifier Supply Voltages

The positive and negative voltage supply rails of the on-board

amplifiers (A0 to A8, A10, U7, and U9) can optionally be set to

+7.5 V or +5 V, and −2.5 V or ground, respectively. The on-board

amplifiers are connected to one of a set of three positive and

three negative supply banks, and the voltage of the banks can be

selected via solder links (shown in Figure 29 and Table 6). These

banks provide users a way of configuring the on-board amplifiers

with different power supply voltages. For example, tying the

amplifier negative supplies to ground, the user can evaluate the

performance of the AD4696 in unipolar supply systems. Table 6

shows the name and default settings of each bank, the solder

link that connects them to the voltage rails, and the amplifiers

powered by each bank.

Note that the symbols for A0 through A7 (ADC drivers) are

split throughout the schematic, such that the amplifier pins are

shown in Figure 26 and Figure 27, whereas the supply pins and

the supply bank solder links are shown in Figure 29.

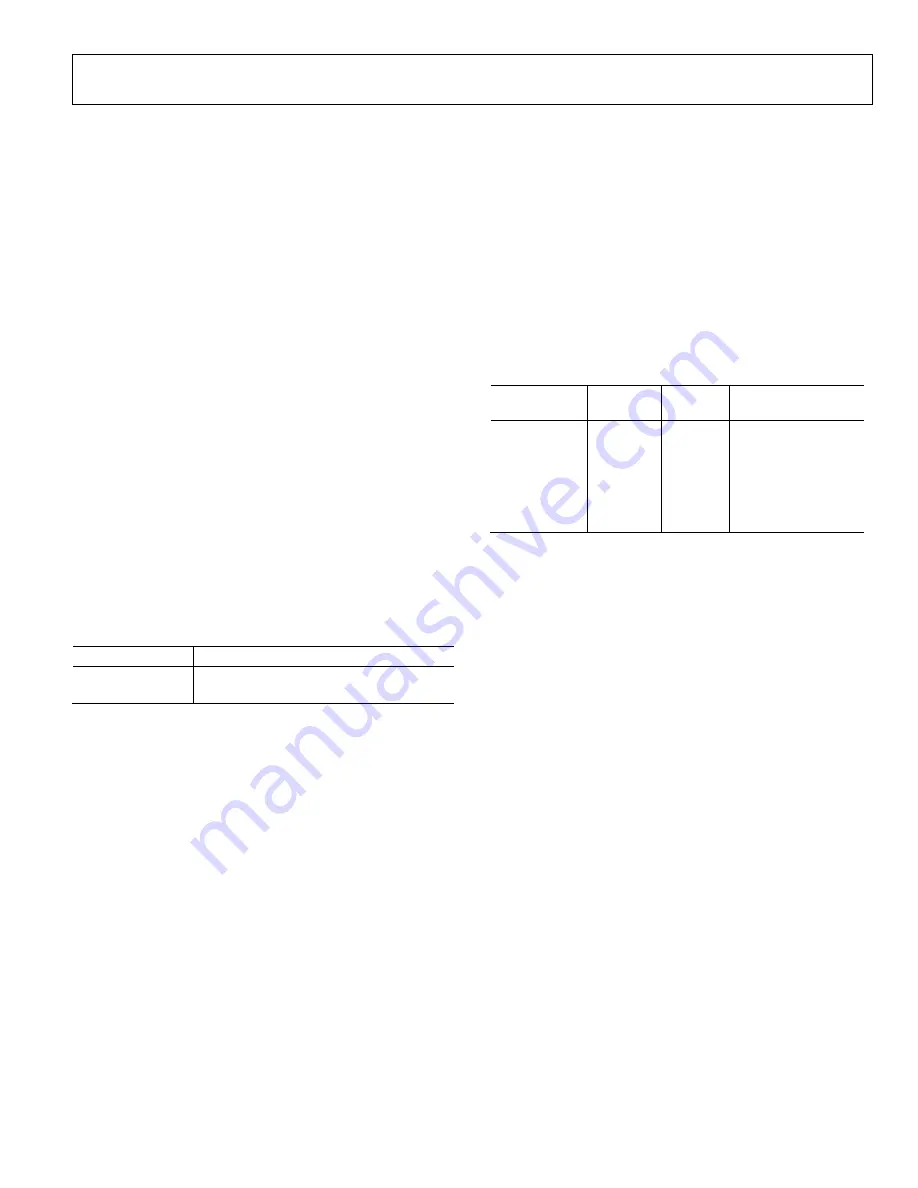

Table 6. Voltage Supply Banks Amplifier Assignments

Supply Bank

Name

Default

Voltage

Solder

Link

Amplifiers

+VS Bank A

7.5 V

JP12

A0, A1, A2, A3

−VS Bank A

−2.5 V

JP13

A0, A1, A2, A3

+VS Bank B

7.5 V

JP14

A4, A5, A6, A7

−VS Bank B

−2.5 V

JP15

A4, A5, A6, A7

+VS Bank C

7.5 V

JP16

A8, A10, U7, U9

−VS Bank C

AGND

JP17

A8, A10, U7, U9

+VS Bank A and –VS Bank A are used to set the supply voltages of

the ADC driver amplifiers for Channel IN0 through Channel IN7

of the AD4696 (A0 through A3). +VS Bank B and –VS Bank B are

used to set the supply voltages of the ADC driver amplifiers for

Channel IN8 through Channel IN15 of the AD4696 (A4 through

A7). +VS Bank C and −VS Bank C are used to set the supply

voltages of the V

REF

/2 amplifier (A8), the reference buffer (A10)

and supply voltages of the dc bias amplifiers (U7 and U9). The

grouping of the power supplies into different voltage supply

banks allows the user to implement different supplies for

different sets of amplifiers, as shown in Table 6.

Power Options for the AD4696

The AD4696 requires an analog supply (AVDD), an ADC core

supply (VDD), and I/O logic supply (VIO). Refer to the AD4696

data sheet for voltage range requirements for each of these supplies.

By default, the AVDD pin is powered by the on-board dual low

dropout (LDO) linear regulator, LT3032 (U5), and the VIO pin

is powered by the on-board 1.8 V LDO regulator, LT1761 (U6).

The VDD (1.8 V) pin of the AD4696 can be powered either

with the AD4696 internal LDO regulator, or alternatively from

the on-board LT1761 (U6). The hardware can be configured for

either of these options via connections between the on-board

supply rails and LDO_IN and VDD inputs.

To power VDD with the AD4696 internal LDO regulator, the

LDO_IN pin must be powered either by an on-board or externally

generated supply, and the VDD pin must be disconnected from any

other device (for example, left floating). The EVAL-AD4696FMCZ

is configured in the factory accordingly, with the LT1761

disconnected from the VDD pin and the LDO_IN pin driven by

LT3032 (U5). In this configuration, the AD4696 internal LDO