ADM-PCIE-8V3 User Manual

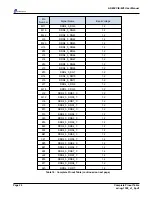

Pin

Number

Signal Name

Bank Voltage

AK15

DDR4_1_DM1

1.2

AP16

DDR4_1_DM2

1.2

AV16

DDR4_1_DM3

1.2

AP21

DDR4_1_DM4

1.2

AU20

DDR4_1_DM5

1.2

AG19

DDR4_1_DM6

1.2

AL18

DDR4_1_DM7

1.2

AG14

DDR4_1_DM8

1.2

AK9

DDR4_1_DQ0

1.2

AK10

DDR4_1_DQ1

1.2

AL13

DDR4_1_DQ10

1.2

AM14

DDR4_1_DQ11

1.2

AL15

DDR4_1_DQ12

1.2

AM17

DDR4_1_DQ13

1.2

AL17

DDR4_1_DQ14

1.2

AM13

DDR4_1_DQ15

1.2

AR15

DDR4_1_DQ16

1.2

AP14

DDR4_1_DQ17

1.2

AT15

DDR4_1_DQ18

1.2

AR14

DDR4_1_DQ19

1.2

AH10

DDR4_1_DQ2

1.2

AP17

DDR4_1_DQ20

1.2

AN16

DDR4_1_DQ21

1.2

AN17

DDR4_1_DQ22

1.2

AN15

DDR4_1_DQ23

1.2

AU15

DDR4_1_DQ24

1.2

AT17

DDR4_1_DQ25

1.2

AV15

DDR4_1_DQ26

1.2

AT16

DDR4_1_DQ27

1.2

AV14

DDR4_1_DQ28

1.2

AW17

DDR4_1_DQ29

1.2

AJ11

DDR4_1_DQ3

1.2

AW14

DDR4_1_DQ30

1.2

AW18

DDR4_1_DQ31

1.2

AP19

DDR4_1_DQ32

1.2

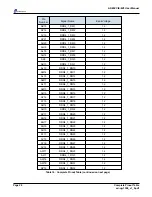

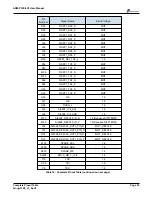

Table 16 : Complete Pinout Table (continued on next page)

Page 26

Complete Pinout Table

ad-ug-1308_v1_9.pdf