ADM-PCIE-8V3 User Manual

3.9 USB Front Panel Interface

For convenience the FPGA can be configured directly from the USB connection on the front panel. The

ADM-PCIE-8V3 utilizes the Digilent USB-JTAG converter box which is supported by the Xilinx software tool suite.

Simply connect a micro-USB AB type cable between the ADM-PCIE-8V3 USB port and a host computer with

Vivado installed. Vivado Hardware Manager will automatically recognize the FPGA and allow you to configure the

FPGA and the BPI configuration PROM.

The same USB connector is used to directly access the system monitor system. All voltages, currents,

temperatures, and non-volatile clock configuration settings can be accessed using Alpha Data's avr2util software

at this interface.

Avr2util is downloadable here:

ftp://ftp.alpha-data.com/pub/firmware/utilities/windows/archive/avr2util-win-2.5.0.zip

The USB driver install file is downloadable here:

ftp://ftp.alpha-data.com/pub/firmware/utilities/windows/archive/avr2_usb_inf.zip

Use "avr2util.exe /?" to see all options.

For example "avr2util.exe /usbcom com4 display-sensors" will desiplay all sensor values.

3.10 Configuration

There are two main ways of configuring the FPGA on the ADM-PCIE-8V3:

•

From Flash memory, at power-on, as described in

Section 3.10.1

•

Using USB cable connected at the front panel USB port

Section 3.10.2

3.10.1 Configuration From Flash Memory

The FPGA can be automatically configured at power-on from a 1 Gbit BPI flash memory device (Micron part

number MT28GU01GAAA1EGC-0SIT). This Flash device is divided into two regions of 64 MiByte each, where

each region is sufficiently large to hold an uncompressed bitstream for a VU095 FPGA.

The ADM-PCIE-8V3 is shipped with a bitstream, corresponding to the "dma_demo" FPGA design from the

ADM-PCIE-8V3 SDK, programmed into region 1 and "reg_access" programmed into region 0. This permits basic

confidence and performance testing to be performed on a board without needing to program anything into the

Flash memory. Alpha Data recommends that region 0 is used as a fallback image; this permits relatively simple

recovery, without requiring direct programming of the FPGA over the front panel USB connection, in the event of

programming a "bad" bitstream into region 1.

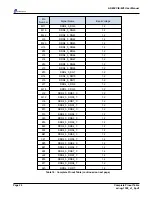

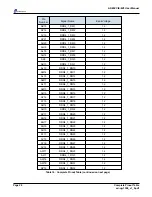

The flash address map is as detailed below:

D

at

a

R

eg

io

n

Region 0

Failsafe

(64 MiB)

Region 1

Default

(64 MiB)

Start Address (Bytes)

0x000_0000

0x400_0000

Figure 12 : Flash Address Map

At power-on, the FPGA attempts to configure itself automatically in BPI mode from region 1 unless the

configuration header on the bitstream ultilizes multi-boot. Multibook and ICAP can be used to selected between

the two configuration regions to be loaded into the FPGA. See Xilinx UG570 MultiBoot for details.

Page 17

Functional Description

ad-ug-1308_v1_9.pdf