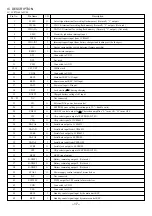

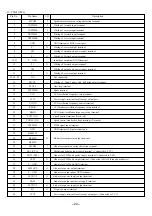

20

Pin No.

Pin Name

I/O

Description

43

NC

I/O

Not connected.

44

PCK

O

VCEC system clock signal output terminal. (Not used)

45

VCC2

Power supply terminal.

46

VSS

Ground terminal.

47

DEFECT

I/O

Defect signal input and output terminal.

48

MD3

I/O

Data input and output terminal to DRAM.

49

NC

I/O

Not connected.

50

MD2

I/O

Data input and output terminal to DRAM.

51

NC

I/O

Not connected.

52

VSS

Ground terminal.

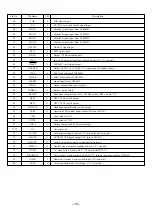

53

MCAS

O

Data input and signal output terminal to DRAM.

54

MOE

O

Data input and signal output terminal to DRAM.

55

MD9

O

Data input and signal output terminal to DRAM. (Not used)

56

MD8

57 ~ 59

S1 ~ S3

O

Sled PWM output terminal.

60

VSS

Ground terminal.

61

VCC2

Power supply terminal.

62

BEMFU

I/O

Sled control signal input and output terminal.

63

VDD

Internal power supply terminal.

64

BEMFV

I

Sled control signal input terminal.

65

BEMFW

66

FOPWMF

O

Focus PWM output terminal.

67

FOPWMR

O

Focus PWM output terminal.

68

TRPWMF

O

Tracking PWM output terminal.

69

TRPWMR

O

Tracking PWM output terminal.

70

FG

I

Speed pulse input terminal.

71

VP

O

LCV servo lock recognition output.

72

FOK

O

Focus OK signal output terminal.

73

FAST

O

FAST signal output terminal. (Not used)

74

CL

I

Data transfer clock input terminal for CPU interface.

75

CE

I

Chip enable signal input terminal for CPU interface.

76

DI

I

Data input terminal for CPU interface.

77

DO

O

Data output terminal for CPU interface.

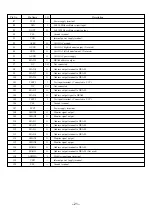

78

WRQ

O

Interrupt signal output terminal for CPU interface.

79

INT

O

Interrupt signal output terminal for CPU interface.

80

FSEQ

O

Frame period detection signal output.

81

F16M

I

16.934 MHz input terminal.

82

ENH

O

De-emphasis indicator output.

83

LRCO

O

LR clock output.

84

DDATA

O

Expanded audio data output.

85

BCO

O

Bit clock output.

86

DDOUT

O

Digital audio output. (Not used)