Manual 104-AIO16A and 104-AIO16E

17

Writing to these addresses will set the Software Gain per channel (see Table 1-1: Analog Input Range

Selection)

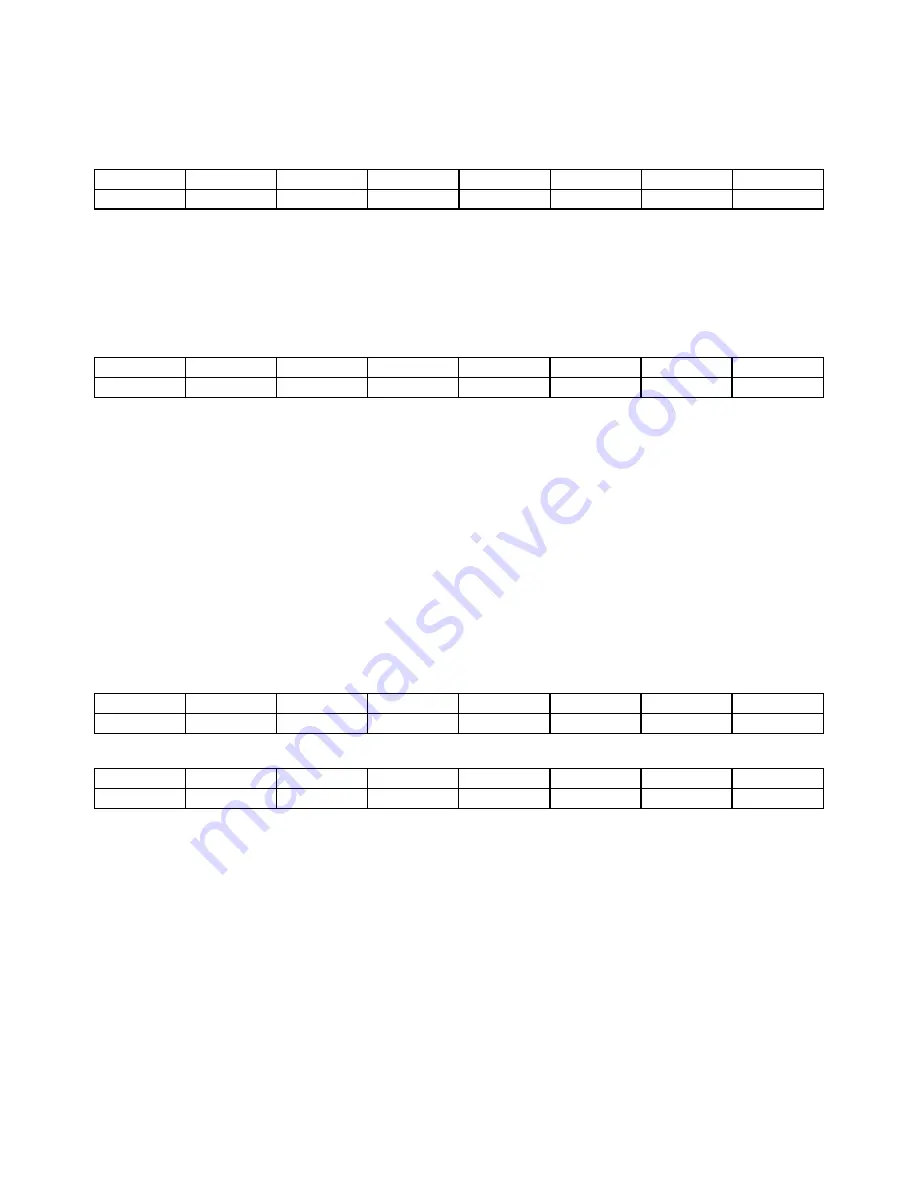

Base A 6

(write)

A/D Start/End Channel Configuration

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

end3 end2 end1 end0 start3 start2 start1 start0

start3-start0 -> A/D start channel (0-15)

end3-end0 -> A/D end channel (0-15)

Writing to this address will set the start and end address of the enabled set of channels.

Base A 7

(write)

A/D Oversample Configuration

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

overSamp7 overSamp6 overSamp5 overSamp4 overSamp3 overSamp2 overSamp1 overSamp0

overSamp7-overSamp0 -> Channel Oversample (0-255)

Writing to this address will set the number of oversamples to take per channel.

Base A 8-B

Counter/Timer Configuration

Counter/Timer 0 is fully programmable for general use. Counter/Timer 1&2 are concatenated together

(output of Counter/Timer 1 is routed to the clock input of Counter/Timer 2). The concatenated

Counter/Timer 1&2 are used for A/D Start: both Timer Start and External Start Trigger. The output of

Counter/Timer 2 is the source for the aforementioned A/D Starts. The output of Counter/Timer 2 is

available on Pin 43 of connector P2.

For detailed information on programming the 8254 Counter/Timer device, please refer to Appendix A.

Base A C-D (write)

DAC 0 Output Data

Base A C

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

da7 da6 da5 da4 da3 da2 da1 da0

Base A D

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

X X X X

da11

da10

da9

da8

da11-da0 -> DAC 0 data

Writing a 12-bit value to this address will output the corresponding voltage on DAC 0 (refer the Option

Selection map for output voltage range). If the DAC simultaneous bit (Base A 10, bit 1) is set,

then DAC 0’s output will update after writing to DAC 1.