PIXIE-4 User’s Manual

V2.69

©

XIA

2015. All rights reserved.

xli

symmetry of the trapezoidal filter, if pulse 2 is rejected because of pulse 3, then pulse 3 is

similarly rejected because of pulse 2.

6.5 Filter Range

To accommodate the wide range of filter rise times from 0.053

s to 106

s, the filters are

implemented in the RTPUs using FPGA configurations with different clock decimations (filter

ranges). The ADC sampling rate is always 13.3ns, but in higher clock decimations, several

ADC samples are averaged before entering the filtering logic. In filter range 1, 2

1

samples are

averaged, 2

2

samples in filter range 2, and so on. Since the sum of rise time and flat top is

limited to 127 decimated clock cycles, filter time granularity and filter time are limited to the

values listed in Table 6.1.

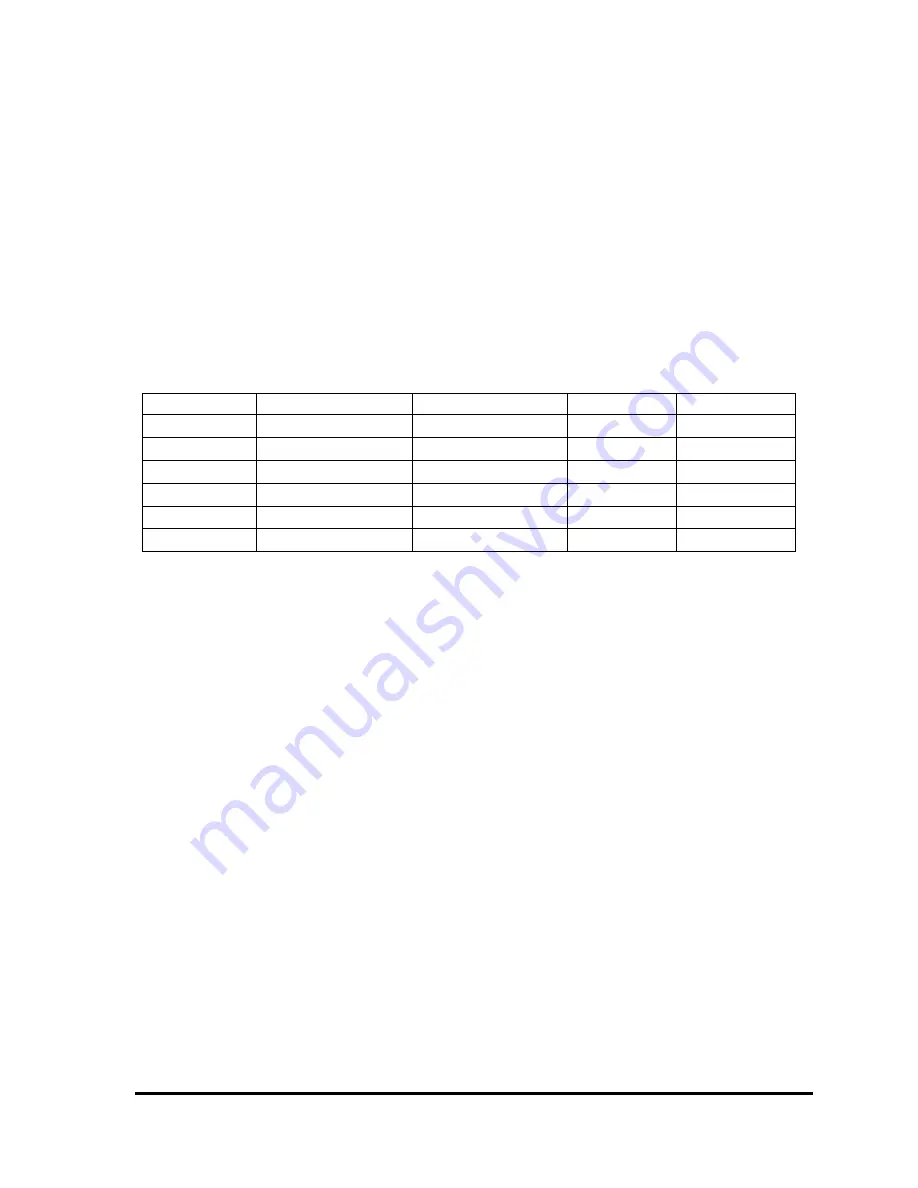

Table 6.1: RTPU clock decimations and filter time granularity

Filter range

Filter granularity max. T

rise

+T

flat

min. T

rise

min. T

flat

1

0.027

s

3.387

s

0.053

s

0.08

s

2

0.053

s

6.773

s

0.107

s

0.16

s

3

0.107

s

13.547

s

0.213

s

0.32

s

4

0.213

s

27.093

s

0.427

s

0.64

s

5

0.427

s

54.187

s

0.853

s

1.28

s

6

0.853

s

108.373

s

1.707

s

2.56

s

All filter ranges are implemented in the same FPGA configuration. Only the

“FILTERRANGE” parameter of the DSP has to be set to select a particular filter range.

6.6 Dead Time and Run Statistics

6.6.1 Definition of dead times

Dead time in the Pixie-4 data acquisition can occur at several processing stages. For the

purpose of this document, we distinguish three types of dead time, each with a number of

contributions from different processes.

6.6.1.1 Dead time associated with each pulse

1. Filter dead time

At the most fundamental level, the energy filter implemented in the FPGA requires a certain

amount of pulse waveform (the “filter time”) to measure the energy. Once a rising edge of a

pulse is detected at time T0, the FPGA computes three filter sums using the waveform data

from T- (a energy filter rise time before T0) to T1 (a flat top time plus filter rise time after T0),

see section 6.4 and figure 6.7. If a second pulse occurs during this time, the energy

measurement will be incorrect. Therefore, processing in the FPGA includes pileup rejection

which enforces a minimum distance between pulses and validates a pulse for recording only if

no more than one pulse occurred from T0 to T1 (in the previous firmware, T- to T1).

Consequently, each pulse creates a dead time Td = (T1 – T0) equal to the filter time. This dead

time, simply given by the time to measure the pulse height, is unavoidable unless pulse height

measurements are allowed to overlap (which would produce false results).