Peripheral

Configuration

Bus

Noise

Filter

Noise

Filter

Clock Prescaler

I2CPSCx

Prescaler

Register

Bit Clock Generator

I2CCLKHx

Clock Divide

High Register

I2CCLKLx

Clock Divide

Low Register

Control

I2CCOARx

Own Address

Register

I2CSARx

Slave Address

Register

I2CCMDRx

Mode Register

I2CEMDRx

Extended Mode

Register

I2CCNTx

Data Count

Register

I2CPID1

Peripheral ID

Register 1

I2CPID2

Peripheral ID

Register 2

T

ransmit

I2CXSRx

Transmit Shift

Register

I2CDXRx

Transmit Buffer

Receive

I2CDRRx

Receive Buffer

I2CRSRx

Receive Shift

Register

I2Cx_SCL

I2Cx_SDA

Interrupt/DMA

I2CIERx

Interrupt Enable

Register

I2CSTRx

Interrupt Status

Register

I2CSRCx

Interrupt Source

Register

Control

I2CPFUNC

Pin Function

Register

I2CPDIR

Pin Direction

Register

I2CPDIN

Pin Data In

Register

I2CPDOUT

Pin Data Out

Register

I2CPDSET

Pin Data Set

Register

I2CPDCLR

Pin Data Clear

Register

Interrupt DMA

Requests

OMAP-L137

SPRS563G – SEPTEMBER 2008 – REVISED JUNE 2014

www.ti.com

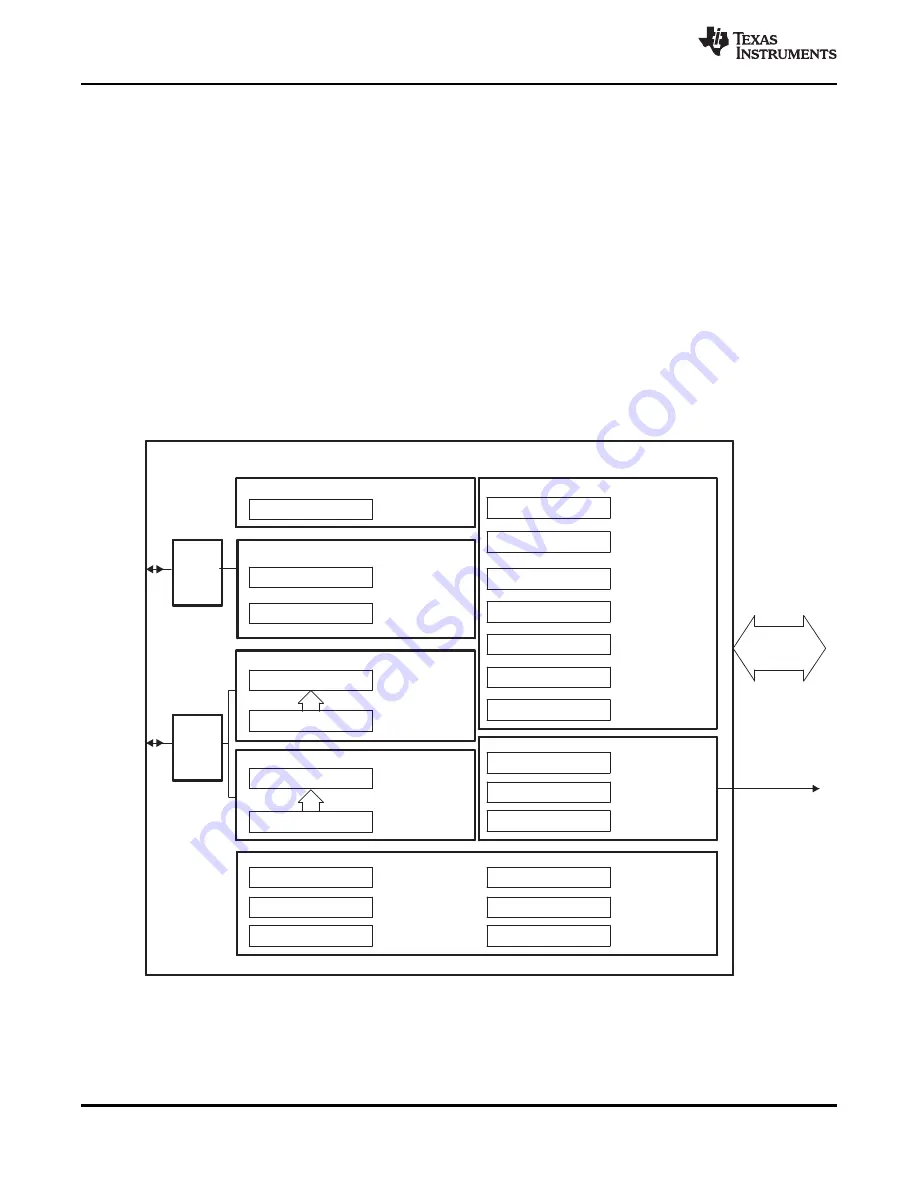

6.23 Inter-Integrated Circuit Serial Ports (I2C0, I2C1)

6.23.1 I2C Device-Specific Information

Having two I2C modules on the OMAP-L137 simplifies system architecture, since one module may be

used by the DSP to control local peripherals ICs (DACs, ADCs, etc.) while the other may be used to

communicate with other controllers in a system or to implement a user interface.

Figure 6-62

is block

diagram of the OMAP-L137 I2C Module.

Each I2C port supports:

•

Compatible with Philips® I2C Specification Revision 2.1 (January 2000)

•

Fast Mode up to 400 Kbps (no fail-safe I/O buffers)

•

Noise Filter to Remove Noise 50 ns or less

•

Seven- and Ten-Bit Device Addressing Modes

•

Master (Transmit/Receive) and Slave (Transmit/Receive) Functionality

•

Events: DMA, Interrupt, or Polling

•

General-Purpose I/O Capability if not used as I2C

Figure 6-62. I2C Module Block Diagram

174

Peripheral Information and Electrical Specifications

Copyright © 2008–2014, Texas Instruments Incorporated

Submit Documentation Feedback

Product Folder Links:

OMAP-L137

Содержание OMAP-L137 EVM

Страница 221: ......