9.3.12 External NTC Monitoring (ADCIN)

The ADCIN pin can be configured through I

2

C to support NTC measurements without the need of an external

biasing circuit. In this mode, the ADCIN pin is biased and monitored in the same manner as the TS pin.

Measurement data can be read by selecting one of the ADC data slots to read the ADCIN.

9.3.13 I

2

C Interface

The BQ25157 device uses a fully compliant I

2

C interface to program and read control parameters, status bits,

and so on. I

2

C is a 2-wire serial interface developed by Philips Semiconductor (see I

2

C-Bus Specification,

Version 2.1, January 2000). The bus consists of a data line (SDA) and a clock line (SCL) with pull-up structures.

When the bus is idle, both SDA and SCL lines are pulled high. All the I

2

C compatible devices connect to the I

2

C

bus through open drain I/O pins, SDA and SCL. A master device, usually a micro-controller or a digital signal

processor, controls the bus. The master is responsible for generating the SCL signal and device addresses. The

master also generates specific conditions that indicate the START and STOP of data transfer. A slave device

receives and/or transmits data on the bus under control of the master device.

The BQ25157 works as a slave and supports the following data transfer modes, as defined in the I

2

C Bus

Specification: standard mode (100 kbps) and fast mode (400 kbps). The interface adds flexibility to the battery

charge solution, enabling most functions to be programmed to new values depending on the instantaneous

application requirements.

Register contents remain intact as long as VBAT or VIN voltages remains above their respective UVLO levels.

The data transfer protocol for standard and fast modes is exactly the same; therefore, they are referred to as the

F/S-mode in this document. The BQ25157 device 7-bit address is 0×6B (shifted 8-bit address is 0xD6).

9.3.13.1 F/S Mode Protocol

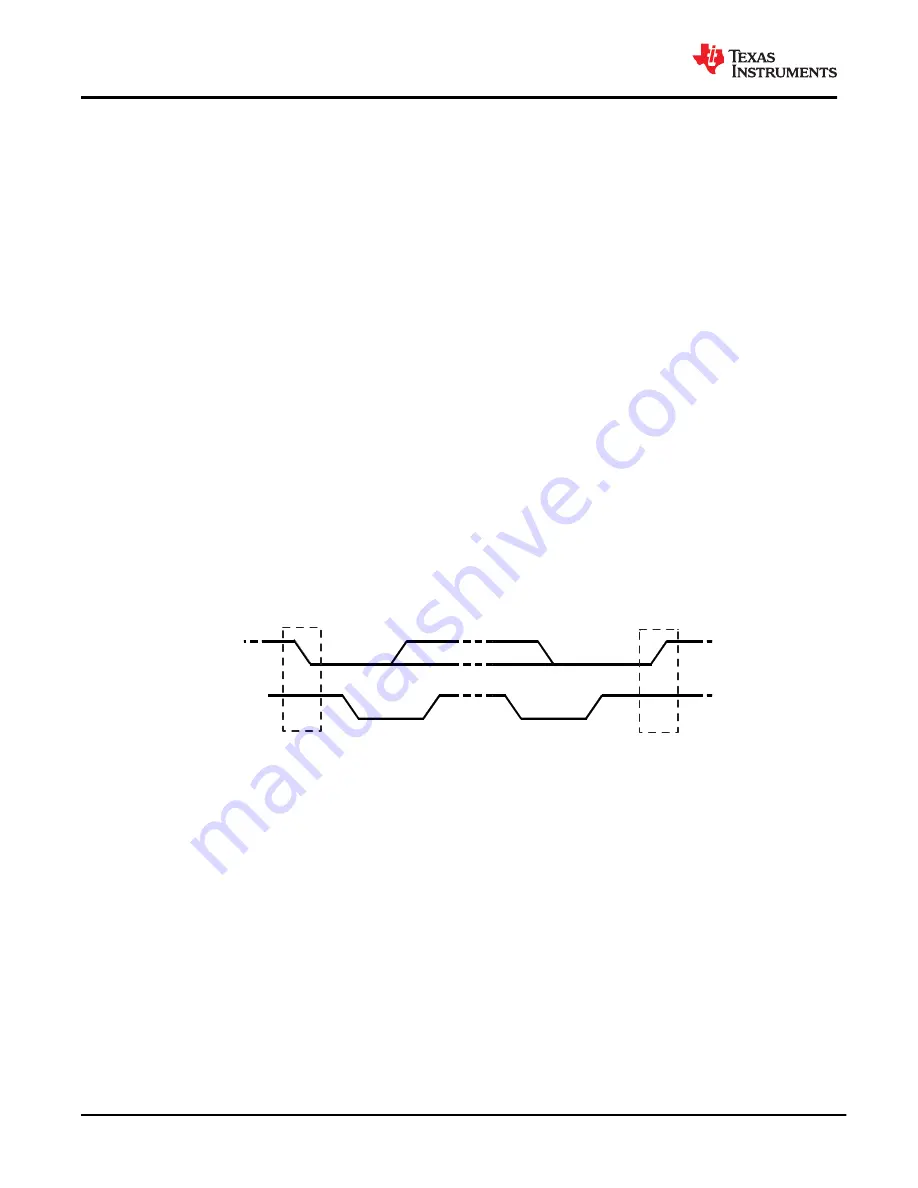

The master initiates data transfer by generating a start condition. The start condition is when a high-to-low

transition occurs on the SDA line while SCL is high, as shown in

. All I

2

C-compatible devices should

recognize a start condition.

START Condition

DATA

CLK

STOP Condition

S

P

Figure 9-9. START and STOP Condition

The master then generates the SCL pulses, and transmits the 8-bit address and the read/write direction bit R/W

on the SDA line. During all transmissions, the master ensures that data is valid. A valid data condition requires

the SDA line to be stable during the entire high period of the clock pulse (see

). All devices recognize

the address sent by the master and compare it to their internal fixed addresses. Only the slave device with a

matching address generates an acknowledge (see

) by pulling the SDA line low during the entire high

period of the ninth SCL cycle. Upon detecting this acknowledge, the master knows that communication link with

a slave has been established.

SLUSEC5 – DECEMBER 2020

32

Copyright © 2020 Texas Instruments Incorporated

Product Folder Links:

Содержание BQ25157

Страница 107: ...D Max E Max 2 045 mm Min 1 645 mm Min 1 985 mm 1 585 mm...

Страница 108: ......

Страница 109: ......