Apollo Carrier Board

User Manual

31

www.terasic.com

September 22, 2020

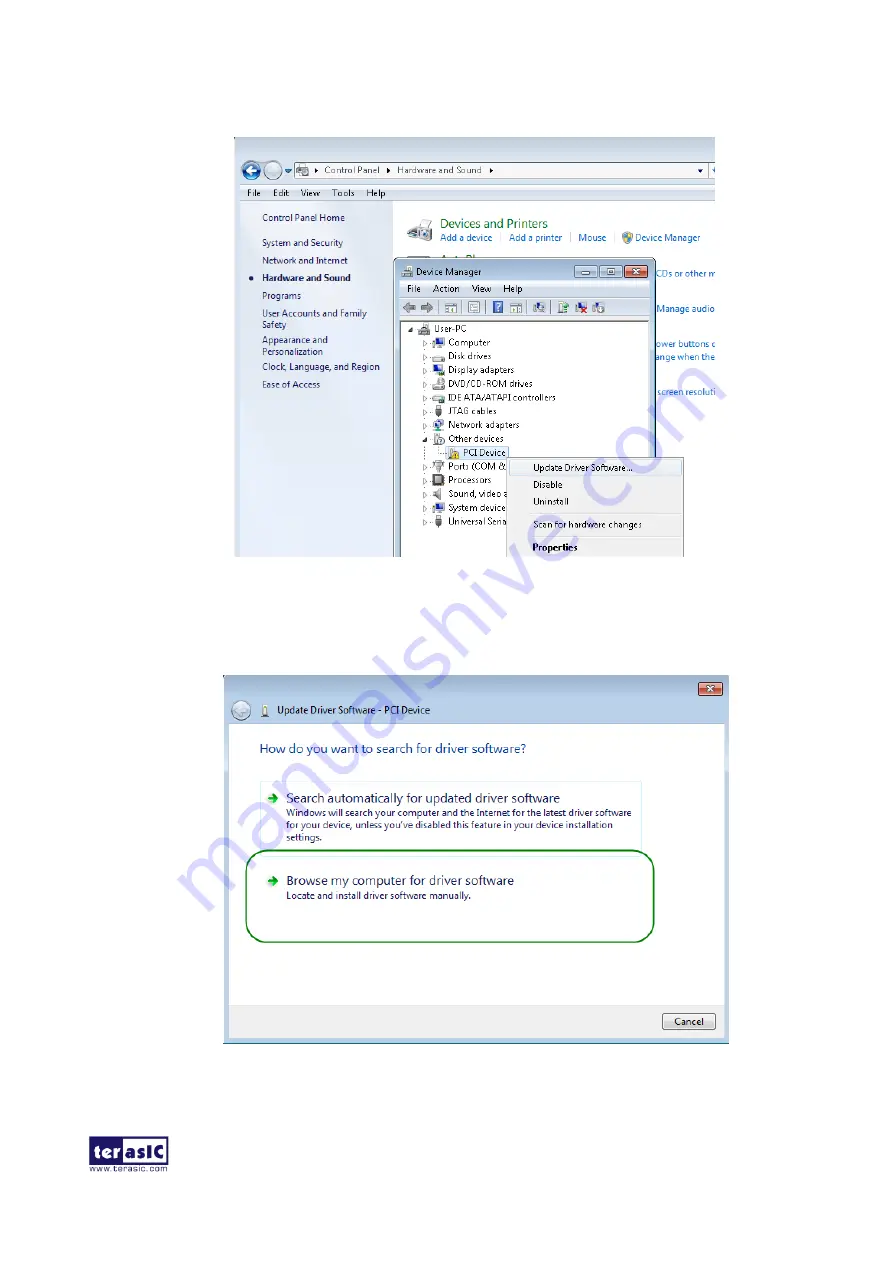

Device

item and right click it to select the Updated Driver Software... items.

Figure 5-3

Screenshot of launching Update Driver Software… dialog

6. In the

How do you want to search for the

driver

software

dialog, click

Browse my

computer for driver software

Figure 5-4 Dialog of Browse my computer for the driver software