6-5

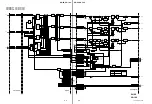

BVP-9500WS/9500WSP MM

6-5

Overall (2/2)

Overall (2/2)

Overall (2/2)

PR-248

X3/X1

X3/X1

CONTROL

S/P

CONV.

IIC-SPM-SDA

IIC-SPM-SCL

HD_REF

VD_REF

IIC_IC1_SDA

R

G

B

SH

(L1)

IE

(L1)

PR

(L1)

PLD

ARC(R.G.B)

PLD

(ARC:Y)

(VF-DTL)

LATCH

D/A

CONV.

W-SHADE_R0-9

W-SHADE_G0-9

W-SHADE_B0-9

EXT-SYNC

EXT-SC

MONITOR-SYNC

4FC

TITLE

TITLE-BACK

L1-R0-11

L1-G0-11

L1-B0-11

10

10

10

12

12

12

12

12

12

SDT

MPX

DTL

DTL_CH

12

12

12

12

10

R

G

B

12

12

12

R-CH

G-CH

B-CH

Y-CH

10

10

10

R-CH

G-CH

B-CH

10

10

10

10

10

10

SRAM

PHASE

CONT.

PHASE

DET.

L.P.F

AMP

30

20

L1_R0-9

L1_G0-9

L1_B0-9

R(X)/G(X)/B(X)/

Y(X)/VF-DTL(X)

18 MHzCLK(X)

CA_SKIN_GATE

CA_VD

CA_HD

H_CONT

H-CONT

BLKG

4:3-ATT

L-ALT

CURSOR

SC

O-BAR

ZEBRA

VF_SKIN_GATE

VTR_SAVE

CHU_DATA

CCU_DATA

BUFFER

BUFFER

FILTER

FILTER

L2[0]-[9]

L3[0]-[9]

10

10

RETTURN_VIDEO

REF_G/H_CONT

B-Y_IN_TRIAX

R-Y_IN_TRIAX

Y_IN_TRIAX

VBS_IN_CA

10

10

10

EN-141

Y AMP

Y VIDEO

Y

BLKG

Y OUT (TRIAX)

R AMP

R VIDEO

R

BLKG

G AMP

G VIDEO

G

BLKG

B AMP

B VIDEO

B

BLKG

Y

R

G

B

R-Y

MATRIX

B-Y

MATRIX

R-Y OUT (TRIAX)

B-Y OUT (TRIAX)

Y

VBS OUT (CA)

R

G

B

Q/U, I/V

MATRIX

ENCODER

CHROMA

SC

OUT

Q

I

BLKG

Q/I BAR

LINE ALTERNATE

SC

REF (G) H COUNT

OSC

SC

SEP.

H CONT

4FSC

EXT SC

EXT SYNC

VF DTL

4:3 ATT

CURSOR

ZEBRA

VF SKIN GATE

CHARACTER

CHARACTER BACK

IIC_SW SDA

IIC_SW_SCL

VF VIDEO

SELECT

R

G

B

Y

SYNC

SEP.

RETURN VIDEO

VF VIDEO

MONITOR SYNC

MONITOR VD

R-Y

MATRIX

B-Y

MATRIX

R

G

B

R

G

B

Y OUT (VF)

R-Y OUT (VF)

B-Y OUT (VF)

MONITOR

RM MONITOR

TEST

WS-WV

WS-WH

WS-RV

WS-RH

FPGA

W-SHADE

WS-R1-9

WS-GI-9

WS-B1-9

10

10

10

10

10

10

SDRAM

X1:ODD

SDRAM

X1:EVEN

DA-143(2/2)

3CH

D/A

CONV.

SERIAL

DATA

CONV.

W SHADE-R(X)

W SHADE-G(X)

W SHADE-B(X)

SER-DATA-1

LD-V-BLKG

SER-CLK

HD REF

VD REF

AD_CLOCK_GATE

AD-PLL-H

IIC I/F

TIMING

GENERATOR

54M-CLOCK GENE

36M-CLOCK GENE

X1:H/V COUNTER

X3:H/V COUNTER

27CLK(X)

36CLK(X)

AT-36CLK(X)

54/18CLK(X)

WS18CLK(X)

3

BUFFER

X3/X1

R_2_L2-R_11_L2

G_0_L2-G_11_L2

B_2_L2-B_11_L2

PR-249

IIC-IC2-SDA

IIC-IC3-SDA

18CLK REF(X)

36CLK(X)

BUFFER

L2/L3

CLOCK

GEN.

X3/X1

SDT

MPX

DTL

10

10

10

10

10

10

10

10

R

G

B

LATCH

L2[0]-[9]

R_2_L3-R_11_L3

G_0_L3-G_11_L3

B_2_L3-B_11_L3

10

10

10

10

10

10

10

10

LATCH

L3[0]-[9]

POWER

ON

RESET

L2

34

68

1

35

34

68

1

35

IIC_SPM_SDA

IIC_SPM_SCL

MIC_X

MIC_Y

UNREG +12V

DC-DC

CONV.

+5.5V

+3.3V

+2.5V

−

5.5V

PS-553

UNREG +12V

DC-DC

CONV.

POWER

DRIVE

+2.5V

−

3.5V

+15.5V

−

11.5V

PS-554

CN-1927

+5V

UNREG +12V

MIC 1

SRC

(L2)

ARC2

(L2)

PR

(L2)

SH

(L2)

IE

(L2)

SH

(L3)

IE

(L3)

PR

(L3)

ARC2

(L3)

SRC

(L3)

L1-G0-9

L1-B0-9

L1-R0-9

CN-1927

CN-1787

4

CA_SKIN_GATE

18MHzCLK(X)

DIGITAL

CA

ANALOG

CA

CA_VD

CA_HD

Содержание BVP-9500WS

Страница 62: ......

Страница 72: ......

Страница 206: ......

Страница 234: ......

Страница 236: ......

Страница 246: ......

Страница 252: ......

Страница 270: ......

Страница 277: ......

Страница 282: ......

Страница 296: ......

Страница 322: ......

Страница 324: ......

Страница 338: ......

Страница 340: ......

Страница 342: ......

Страница 346: ......

Страница 350: ......

Страница 356: ......

Страница 358: ......

Страница 360: ......

Страница 362: ......

Страница 368: ......

Страница 372: ......

Страница 378: ......

Страница 380: ......

Страница 382: ......

Страница 389: ......

Страница 390: ...Printed in Japan Sony Corporation 2002 9 08 B P Company 2001 BVP 9500WS J UC BVP 9500WSP CE J E 9 968 580 02 ...