SN8P2318 Series

C-type LCD, RFC 8-Bit Micro-Controller

SONiX TECHNOLOGY CO., LTD

Page 85

Version 1.5

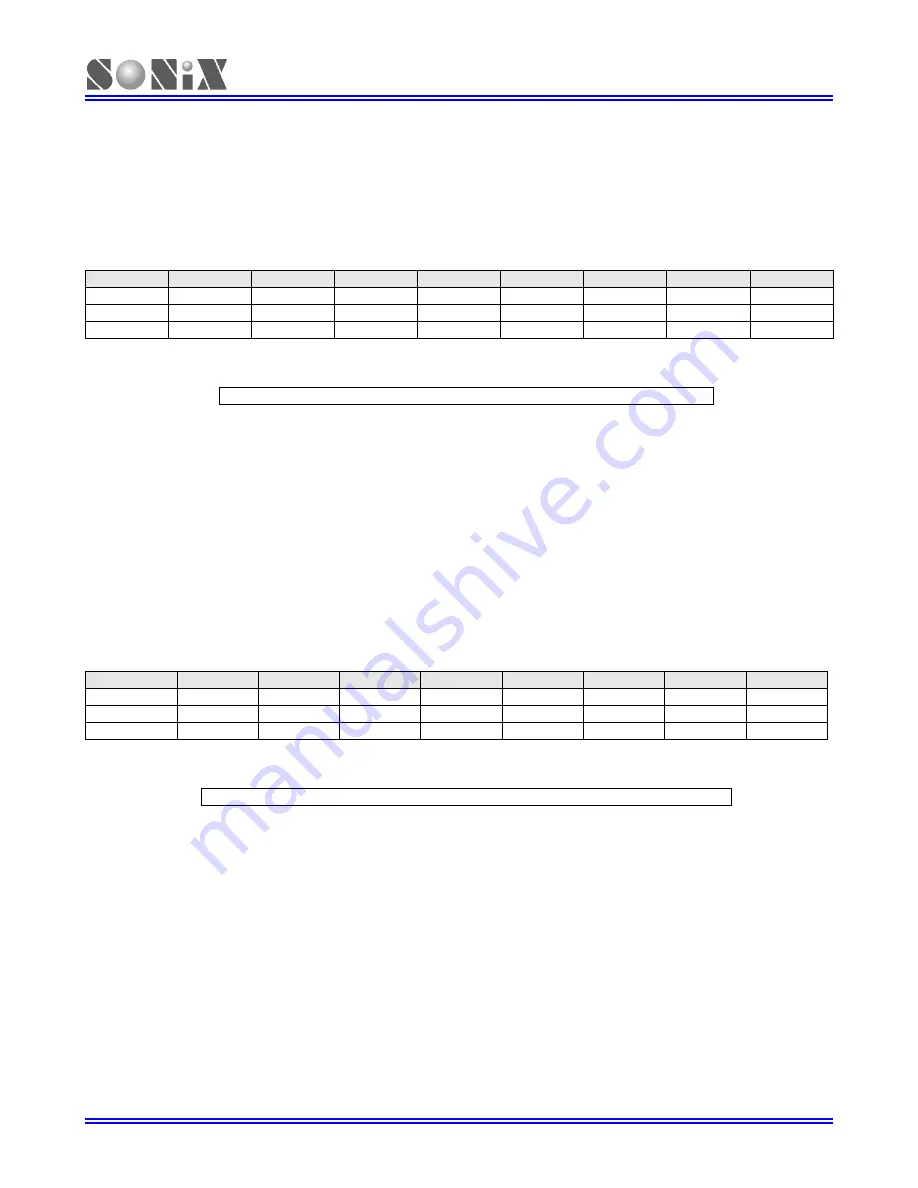

8.3.5 TC0R AUTO-RELOAD REGISTER

TC0 timer builds in auto-reload function, and TC0R register stores reload data. When TC0C overflow occurs, TC0C

register is loaded data from TC0R register automatically. Under TC0 timer counting status, to modify TC0 interval time

is to modify TC0R register, not TC0C register. New TC0C data of TC0 interval time will be updated after TC0 timer

overflow occurrence, TC0R loads new value to TC0C register. But at the first time to setup TC0M, TC0C and TC0R

must be set the same value before enabling TC0 timer. TC0 is double buffer design. If new TC0R value is set by

program, the new value is stored in 1

st

buffer. Until TC0 overflow occurs, the new value moves to real TC0R buffer.

This way can avoid any transitional condition to effect the correctness of TC0 interval time and PWM output signal.

0CDH

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

TC0R

TC0R7

TC0R6

TC0R5

TC0R4

TC0R3

TC0R2

TC0R1

TC0R0

Read/Write

W

W

W

W

W

W

W

W

After reset

0

0

0

0

0

0

0

0

The equation of TC0R initial value is as following.

TC0R initial value = 256 - (TC0 interrupt interval time * TC0 clock rate)

Example: To calculation TC0C and TC0R value to obtain 10ms TC0 interval time. TC0 clock source is

Fcpu = 16MHz/16 = 1MHz. Select TC0RATE=000 (Fcpu/128).

TC0 interval time = 10ms. TC0 clock rate = 16MHz/16/128

TC0C/TC0R initial value = 256 - (TC0 interval time * input clock)

= 256 - (10ms * 16MHz / 16 / 128)

= 256 - (10

-2

* 16 * 10

6

/ 16 / 128)

= B2H

8.3.6 TC0D PWM DUTY REGISTER

TC0D register

’s purpose is to decide PWM duty. In PWM mode, TC0R controls PWM’s cycle, and TC0D controls the

duty of PWM. The operation is base on timer counter value. When TC0C = TC0D, the PWM high duty finished and

exchange to low level. It is easy to configure TC0D to choose the right PWM

’s duty for application.

0E8H

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

TC0D

TC0D7

TC0D6

TC0D5

TC0D4

TC0D3

TC0D2

TC0D1

TC0D0

Read/Write

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

After Reset

0

0

0

0

0

0

0

0

The equation of TC0D initial value is as following.

TC0D initial value = TC0R + (PWM high pulse width period / TC0 clock rate)

Example: To calculate TC0D value to obtain 1/3 duty PWM signal. The TC0 clock source is Fcpu =

16MHz/16= 1MHz. Select TC0RATE=000 (Fcpu/128).

TC0R = B2H. TC0 interval time = 10ms. So the PWM cycle is 100Hz. In 1/3 duty condition, the high pulse width is

about 3.33ms.

TC0D initial value = B2H + (PWM high pulse width period / TC0 clock rate)

= B2H + (3.33ms * 16MHz / 16 / 128)

= B2H + 1AH

= CCH