Hardware Design Specification

ASD-B-16-0247 Rev1.3

Page 18 of 105

September 8, 2017

RTK00V2XRC7746SFS

DDR3-1000. The Tethys board can support memory size up to 2GB (8-Gbit memory x 2) and the data bus width is 32 bits x1. The

DDR3-SDRAMs are allocated to the address space from H'01_0000 0000 to H'01_FFFF FFFF in the R-Car W2H. The address

ranges from H'00_40000000 to H'00_BFFF FFFF can be accessed by default as a mirror area of H'01_0000 0000 to H'01_7FFF

FFFF.

Table 4 DDR3-SDRAM Interface Specifications

Controller

On-chip external bus controller for DDR3-SDRAM (DBSC) in the R-Car W2H

Product name

MT41K256M16HA-125 AAT:E from Micron

DDR3-1600 (x 16 bits, 4 Gbits) x 2 pcs

Power supply voltage

1.50 V

Capacity

H'01_0000 0000 to H'01_FFFF FFFF

Bus width

32-bit data bus

Memory bus frequency(R-Car W2H Spec.)

DDR3-1000

3.2.2

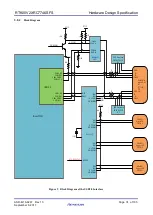

Signal Connections between R-Car W2H and DDR3-SDRAMs

Table 5 Signal Connections between R-Car W2H and DDR3-SDRAMs

R-Car W2H

DDR3-SDRAM (U3)

DDR3-SDRAM (U4)

D[31:16]

D[15:0]

M0DQ[31:16]

DQ[15:0]

--

M0DQ[15:0]

--

DQ[15:0]

M0A[15:0]

A[15:0]

←

M0BA[2:0]

BA[2:0]

←

M0CK1

、

M0CK1#

CK

、

CK#

--

M0CK0

、

M0CK0#

--

CK

、

CK#

MCKE1

CKE

--

MCKE0

--

CKE

M0CS1#

CS#

--

M0CS0#

--

CS#

M0WE#

WE#

←

M0RAS#

RAS#A

←

M0CAS#

CAS#

←

M0DQS3

、

M0DQS3#

UDQS

、

UDQS#

--

M0DQS2

、

M0DQS2#

LDQS

、

LDQS#

--

M0DQS1

、

M0DQS1#

--

UDQS

、

UDQS#

M0DQS0

、

M0DQS0#

--

LDQS

、

LDQS#

M0DM3

、

M0DM2

UDM

、

LDM

--

M0DM1

、

M0DM0

--

UDM

、

LDM