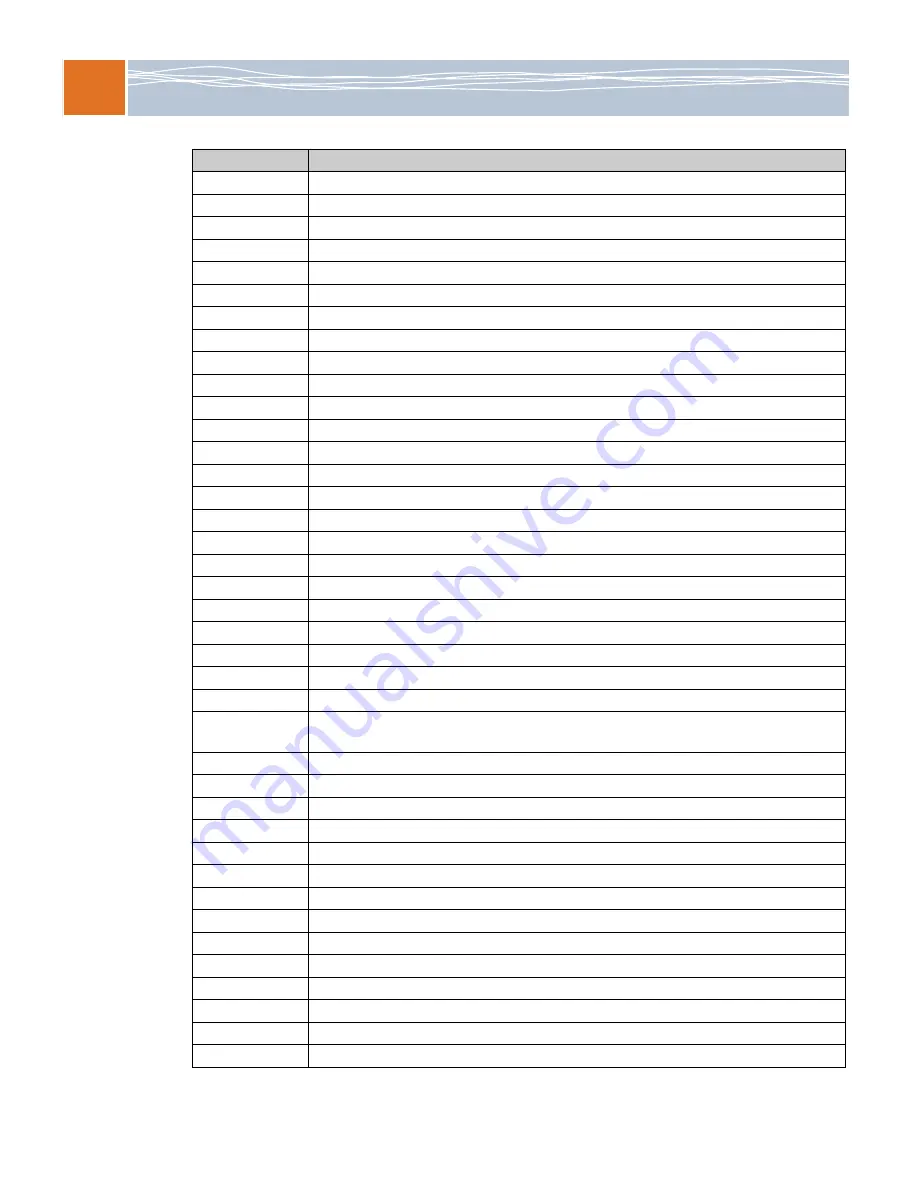

B

System resources

64

17h

Initializes external cache before memory auto size.

18h

Initializes the timers.

1Ah

Tests the DMA registers.

1Ch

Initializes interrupt controllers for some shutdowns.

20h

Verifies DRAM refresh.

22h

Initializes the Keyboard Controller for Keyboard Test.

24h

Sets 4GB segments for DS,ES,FS,GS,SS.

28h

Sizes DRAM.

29h

Initializes the POST Memory Manager.

2Ah

Zeroes the RAM up to the minimum RAM specified in the chipset RAM table.

2Ch

Tests address lines of the RAM.

2Eh

Tests the first 4MB of RAM.

2Fh

Initializes external cache before shadowing.

32h

Computes CPU clock speed in MHz.

33h

Initializes the Phoenix Dispatch Manager.

34h

Tests the CMOS RAM and RTC (S2D)

36h

Vector to the proper shutdown routine.

38h

Shadows system BIOS ROM.

3Ah

Auto sizes the external cache.

3Ch

Advanced chipset configuration.

3Dh

Alternates register configuration.

42h

Initializes interrupt vectors.

45h

POST device initialization.

46h

Verifies that the copyright message is intact.

48h

Verifies the hardware configuration and notes whether the system has color or monochrome

video.

49h

Initializes the Plug and Play, and PCI.

4Ah

Initializes the video device.

4Bh

Initializes QuietBoot (splash screen).

4Ch

Shadows video BIOS ROM.

4Eh

Displays the copyright message.

4Fh

Allocates storage for Multiboot tables.

50h

Displays the CPU type and speed.

52h

Initializes and Configures the Keyboard & PS/2 Mouse.

55h

Configures USB devices.

58h

Tests hot interrupts

59h

Initializes the POST display service.

5Ah

Displays “Press F2 for Setup“prompt.

5Bh

Disables L1 cache.

5Ch

Determines size of conventional memory.

Checkpoint Code Description

Содержание PL35Q

Страница 1: ...www radisys com PROCELERANT ENDURA Q35 MOTHERBOARD PRODUCT MANUAL 007 03198 0000 December 2007 PL35Q ...

Страница 6: ...6 ...

Страница 8: ...8 ...

Страница 20: ...2 Product Specification 20 ...

Страница 38: ...3 Hardware Reference 38 ...

Страница 58: ...A Connector Description 58 ...

Страница 72: ...C 72 ...