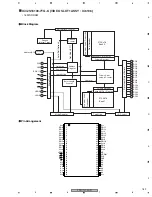

PRO-1010HD

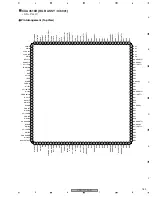

179

5

6

7

8

5

6

7

8

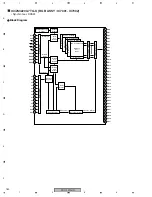

C

D

F

A

B

E

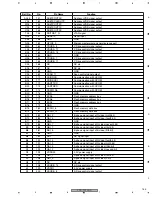

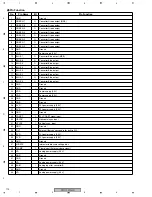

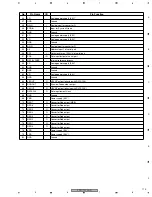

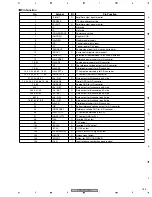

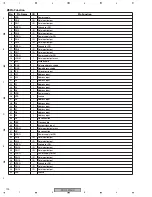

No.

Pin Name

Pin Function

1

HSCTL

HDRV output

Used to select whether to output the VDRV section of the HDRV output signal.

High : VDRV section of HDRV is output

Low : VDRV section of HDRV is not output

2

C/HSYNC IN

Composite sync / H SYNC input

Input either the composite synchronization signal or the horizontal synchronization signal.

Input is clamped, and is initiated by capacitor coupling.

3

VIDEO IN

SYNC ON VIDEO input

Inputs the SYNC ON VIDEO signal(green).

Input is sink chip clamped.

Input is initiated by capacitor coupling.

4

VSEPA

f-V conversion

Converts the horizontal synchronization signal frequency into a voltage.

The voltage generated is proportional to the frequency of the horizontal synchronization signal.

Attach a 0.56

µ

F capacitor between the ground pins.

5

VSYNC IN

V SYNC input Inputs the vertical synchronization signal.

6

CVPOL

Vertical polarity integration

Integrates the vertical synchronization signal polarity detection circuit.

Attach a 1.5

µ

F capacitor between this pin and the ground.

7

CVEXI

Vertical existence integration

Integrates the vertical synchronization signal existence detection circuit.

Attach a 1

µ

F capacitor between this pin and the ground.

8

CPSEL

Setting the clamp position

Used to set the clamp pulse generation position to either the front or back edge of HSYNC

High : The front edge is the generation position

Open : Composite / H SYNC IN : The front edge is the generation position

VIDEO IN : The back edge is the generation position

Low

: The back edge is the generation position

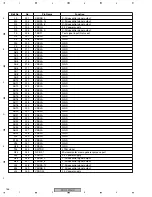

9

GND

Ground

10

CPWID

Setting the clamp pulse width

Sets the clamp pulse width according to the attached time constant.

Attach a resistor between this pin and VCC and, a capacitor between this pin and GND.

When R = 3.9k

Ω

and C = 100pF, pulse width is approximately 400 ns.

Set the resistor to register an abnormality at 1k

Ω

.

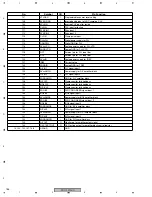

11

VDRV

VDRV output

Outputs the vertical synchronization signal.

The output signal has positive polarity.

12

CLAMP

Clamp output

Outputs the clamp pulse generated from the vertical synchronization signal.

The output signal has a positive polarity.

13

HDRV

HDRV output

Outputs the clamp pulse generated from the horizontal synchronization signal.

The output signal has positive polarity.

14

Vcc

Power supply

15

EXIV

Vertical existence output

Indecates whether the vertical synchronization signal exists.

16

POLV

Vertical polarity output

Indicates the polarity of the vertical synchronization signal.

17

EXIH

Horizontal existence output

Indicates whether the horizontal synchronization signal exists.

18

POLH

Horizontal polarity output

Indicates the polarity of the horizontal synchronization signal.

Pin Function