Circuit Descriptions

EN 38

7.

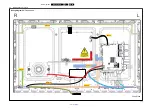

Figure 7-4 Marvell BG-Q2 Architecture FHD100

19570_161_140721.eps

14-07-21

Marvell BG2-Q Architecture FHD100

GLUE

GLUE

GLUE

G

G

LUE

eMMC

4GB

AL-SPI

FRC

NT72314

FHD 100Hz

SPI

swtich

AL-SPI/Ctrl

AL-SPI

Hybrid

tuner

CiMax

TS-in

TS-in

USB2.0

S-Tuner

USB

2 Wifi

USB2.0

USB3.0

ETH

USB

2 Wifi

USB

2 Wifi

U

U

U

U

U

U

U

U

U

S

SB

SB

SB

SB

SB

SB

SB

2

2

2

W

W

W

i

i

i

f

f

f

i

i

i

U

U

SB

SB

2

2

W

W

i

i

f

f

i

i

U

SB

2

W

ifi

USB

11n 2x2

TS-out

2x DDR3

1600

4Gb

32

2x DDR3

1600

4Gb

32

GLUE

GLUE

GLUE

CVBS

RGB

YPbPr

SPDIF

GLUE

GLUE

GLUE

GLUE

Audio L/R

IF

G

G

G

L

L

L

U

U

U

E

E

E

G

G

G

L

L

U

U

E

E

G

G

LUE

G

L

U

E

GL

U

E

G

G

G

G

G

G

G

G

L

L

L

L

L

L

L

L

U

U

U

U

U

U

U

U

E

E

E

E

E

E

E

E

Analog

demod.

TTL

SPDIF

I2S

FPGA

LX75

=Anaconda

Noise

reduction

Local contrast

DDR3

1600

2Gb

16

2x DDR3

1600

2Gb

32

GLUE

GLUE

GLUE

G

G

LU

U

E

G

G

GL

L

U

U

E

E

G

G

G

G

G

L

L

L

U

U

U

E

E

E

G

G

L

L

U

U

E

E

HDMI

4 to 1

UART

I2S

LR

Audio

AMP

SPI

3D-LR 3D-LR

SplashscreenOn

I2S

I2S

Wifi

HUB

DVB-

T/C/S/

T2/C2/S2

DVB-

T/C/S/

T2/C2/S2

BG2-Q

Quad Core A9

4x16bit DDR3

Cypress C0

BL-PWM (8

3D-Goggle

Disp-Ctr (4

BL-Boost

3D-LR