CHAPTER 1 GENERAL (

µ

PD789860 SUBSERIES)

User’s Manual U14826EJ5V0UD

23

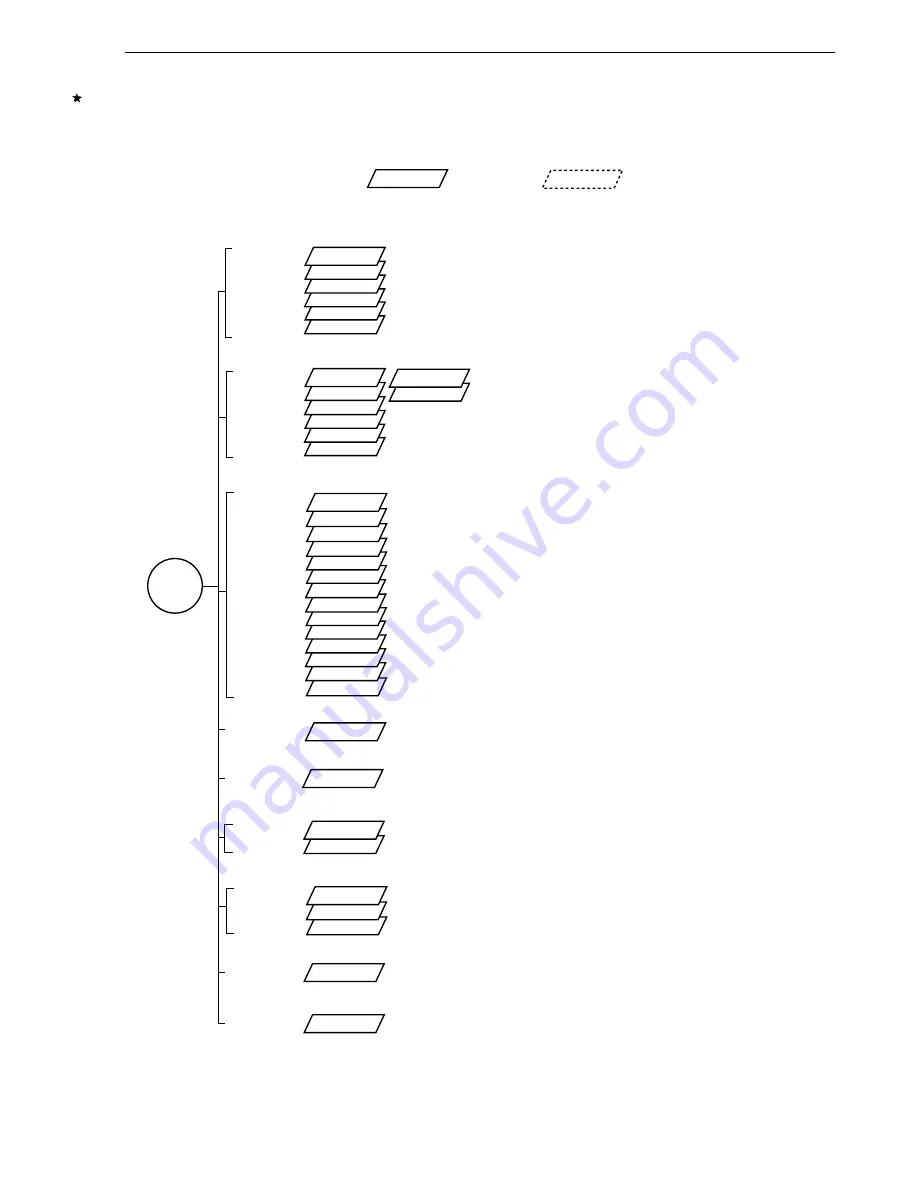

1.6 78K/0S Series Lineup

The products in the 78K/0S Series are listed below. The names enclosed in boxes are subseries names.

Products under

development

Products in mass

production

Y subseries supports SMB.

52-pin

SIO + resistance division method LCD (24

×

4)

8-bit A/D + internal voltage boosting method LCD (23

×

4)

PD789327

LCD drive

80-pin

80-pin

PD789436

PD789446

PD789426

PD789456

PD789417A

PD789407A

PD789316

PD789467

PD789306

PD789426 with 10-bit A/D

PD789446 with 10-bit A/D

SIO + 8-bit A/D + resistance division method LCD (28

×

4)

SIO + 8-bit A/D + internal voltage boosting method LCD (15

×

4)

PD789407A with 10-bit A/D

SIO + 8-bit A/D + internal voltage boosting method LCD (5

×

4)

RC oscillation version of PD789306

SIO + internal voltage boosting method LCD (24

×

4)

64-pin

64-pin

52-pin

64-pin

64-pin

64-pin

SIO + 10-bit A/D + internal voltage boosting method LCD (28

×

4)

80-pin

SIO + 8-bit A/D + resistance division method LCD (28

×

4)

80-pin

PD789479

PD789489

64-pin

Small-scale package, general-purpose applications

78K/0S

Series

On-chip UART and capable of low-voltage (1.8 V) operation

PD789074 with subsystem clock added

Inverter control

44-pin

PD789842

On-chip inverter controller and UART

44-pin

Small-scale package, general-purpose applications and A/D function

44-pin

PD789167 with 10-bit A/D

PD789104A with enhanced timer

PD789177Y

PD789167Y

USB

88-pin

PD789830

PD789835

144-pin

UART + dot LCD (40

×

16)

UART + 8-bit A/D + dot LCD (total display outputs: 96)

42-/44-pin

44-pin

30-pin

20-pin

20-pin

PD789026 with enhanced timer function

RC oscillation version of PD789052

VFD drive

52-pin

64-pin

PD789871

On-chip VFD controller (total display outputs: 25)

Meter control

PD789881

UART + resistance division method LCD (26

×

4)

30-pin

PD789074 with enhanced timer function and expanded ROM and RAM

44-pin

PD789800

For PC keyboard. On-chip USB function

Keyless entry

20-pin

20-pin

30-pin

On-chip POC and key return circuit

RC oscillation version of PD789860

On-chip bus controller

On-chip CAN controller

µ

µ

µ

PD789074

PD789088

PD789062

PD789046

PD789026

PD789052

µ

µ

µ

µ

µ

µ

µ

µ

µ

µ

PD789860

PD789861

PD789862

µ

µ

µ

µ

µ

µ

µ

µ

µ

µ

µ

µ

µ

µ

µ

30-pin

PD789850A

µ

µ

µ

µ

µ

µ

PD789860 without EEPROM, POC, and LVI

µ

µ

µ

µ

30-pin

30-pin

30-pin

30-pin

PD789124A

PD789134A

PD789104A

PD789114A

PD789124A with 10-bit A/D

RC oscillation version of PD789104A

PD789104A with 10-bit A/D

PD789026 with 8-bit A/D and multiplier added

µ

µ

µ

µ

µ

µ

µ

µ

µ

µ

µ

PD789860 with enhanced timer function, SIO, and expanded ROM and RAM

µ

µ

µ

PD789167

PD789177

µ

44-pin

PD789852

µ

PD789850A with enhanced timer and A/D converter, etc.

µ

µ

Remark

VFD (Vacuum Fluorescent Display) is referred to as FIP

TM

(Fluorescent Indicator Panel) in some

documents, but the functions of the two are the same.

Содержание PD789860

Страница 2: ...User s Manual U14826EJ5V0UD 2 MEMO ...