EXCEPTION PROCESSING STATE (INTERRUPT PROCESSING)

MOTOROLA

PROCESSING STATES

7 - 21

There are two cases in which the stacked address will not point to the illegal instruction:

1. If the illegal instruction is one of the two instructions at an interrupt vector loca-

tion and is fetched during a regular interrupt service, the processor will stack

the address of the next sequential instruction in the normal instruction flow (the

regular return address of the interrupt routine that had the illegal opcode in its

vector).

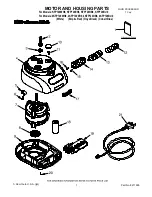

2. If the illegal instruction follows an REP instruction (see Figure 7-6), the proces-

sor will effectively execute the illegal instruction as a repeated NOP and the

interrupt vector will then be inserted in the pipeline. The next instruction will be

fetched but will not be decoded or executed. The processor will stack the

address of the next sequential instruction, which is two instructions after the

illegal instruction.

In DO loops, if the illegal instruction is in the loop address (LA) location and the instruc-

tion preceding it (i.e., at LA-1) is being interrupted, the loop counter (LC) will be decre-

mented as if the loop had reached the LA instruction. When the interrupt service ends

and the instruction flow returns to the loop, the illegal instruction will be refetched (since

it is the next sequential instruction in the flow). The loop state machine will again decre-

ment LC because the LA instruction is being executed. At this point, the illegal instruction

will trigger the III. The result is that the loop state machine decrements LC twice in one

loop due to the presence of the illegal opcode at the LA location.

INTERRUPT CONTROL CYCLE 1

i

INTERRUPT CONTROL CYCLE 2

i

FETCH

n1

n2

n3

n4

n5

n6

n7

—

—

—

ii1

ii2

n8

DECODE

n1

n2

n3

n4

REP

II

—

—

—

—

ii1

ii2

n8

EXECUTE

n1

n2

n3

n4

REP

REP

NOP

—

—

—

ii1

ii2

n8

INSTRUCTION CYCLE COUNT

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

i

= INTERRUPT

ii

= INTERRUPT INSTRUCTION WORD

II

= ILLEGAL INSTRUCTION

n

= NORMAL INSTRUCTION WORD

ILLEGAL INSTRUCTION INTERRUPT

RECOGNIZED AS PENDING

Figure 7-6 Repeated Illegal Instruction

Содержание DSP56K

Страница 12: ...xii LIST of TABLES MOTOROLA List of Tables Continued Table Page Number Title Number ...

Страница 13: ...MOTOROLA DSP56K FAMILY INTRODUCTION 1 1 SECTION 1 DSP56K FAMILY INTRODUCTION ...

Страница 25: ...MOTOROLA DSP56K CENTRAL ARCHITECTURE OVERVIEW 2 1 SECTION 2 DSP56K CENTRAL ARCHITECTURE OVERVIEW ...

Страница 31: ...MOTOROLA DATA ARITHMETIC LOGIC UNIT 3 1 SECTION 3 DATA ARITHMETIC LOGIC UNIT ...

Страница 50: ...DATA ALU SUMMARY 3 20 DATA ARITHMETIC LOGIC UNIT MOTOROLA ...

Страница 51: ...MOTOROLA ADDRESS GENERATION UNIT 4 1 SECTION 4 ADDRESS GENERATION UNIT ...

Страница 77: ...MOTOROLA PROGRAM CONTROL UNIT 5 1 SECTION 5 PROGRAM CONTROL UNIT ...

Страница 124: ...INSTRUCTION GROUPS 6 30 INSTRUCTION SET INTRODUCTION MOTOROLA ...

Страница 125: ...MOTOROLA PROCESSING STATES 7 1 SECTION 7 PROCESSING STATES STOP WAIT EXCEPTION NORMAL RESET ...

Страница 167: ...STOP PROCESSING STATE MOTOROLA PROCESSING STATES 7 43 ...

Страница 168: ...STOP PROCESSING STATE 7 44 PROCESSING STATES MOTOROLA ...

Страница 169: ...MOTOROLA PORT A 8 1 SECTION 8 PORT A ...

Страница 176: ...PORT A INTERFACE 8 8 PORT A MOTOROLA ...

Страница 177: ...MOTOROLA PLL CLOCK OSCILLATOR 9 1 SECTION 9 PLL CLOCK OSCILLATOR x x d Φ VCO ...

Страница 191: ...10 2 ON CHIP EMULATION OnCE MOTOROLA SECTION 10 ON CHIP EMULATION OnCE ...

Страница 218: ...USING THE OnCE MOTOROLA ON CHIP EMULATION OnCE 10 29 ...

Страница 604: ...INSTRUCTION ENCODING A 338 INSTRUCTION SET DETAILS MOTOROLA ...

Страница 605: ...MOTOROLA BENCHMARK PROGRAMS B 1 APPENDIX B BENCHMARK PROGRAMS T T T T T P1 P3 P2 P4 T T T ...

Страница 606: ...SECTION CONTENTS B 2 BENCHMARK PROGRAMS MOTOROLA SECTION B 1 INTRODUCTION 3 SECTION B 2 BENCHMARK PROGRAMS 3 ...

Страница 609: ...BENCHMARK PROGRAMS MOTOROLA BENCHMARK PROGRAMS B 5 ...

Страница 611: ...BENCHMARK PROGRAMS MOTOROLA BENCHMARK PROGRAMS B 7 ...

Страница 613: ...BENCHMARK PROGRAMS MOTOROLA BENCHMARK PROGRAMS B 9 ...

Страница 615: ...BENCHMARK PROGRAMS MOTOROLA BENCHMARK PROGRAMS B 11 ...