REL1.1

Page 33 of 89

iWave Systems Technologies Pvt. Ltd.

Zynq-Ult MPSoC SOM Development Platform Hardware User Guide

2.4.6

CAN0 Header

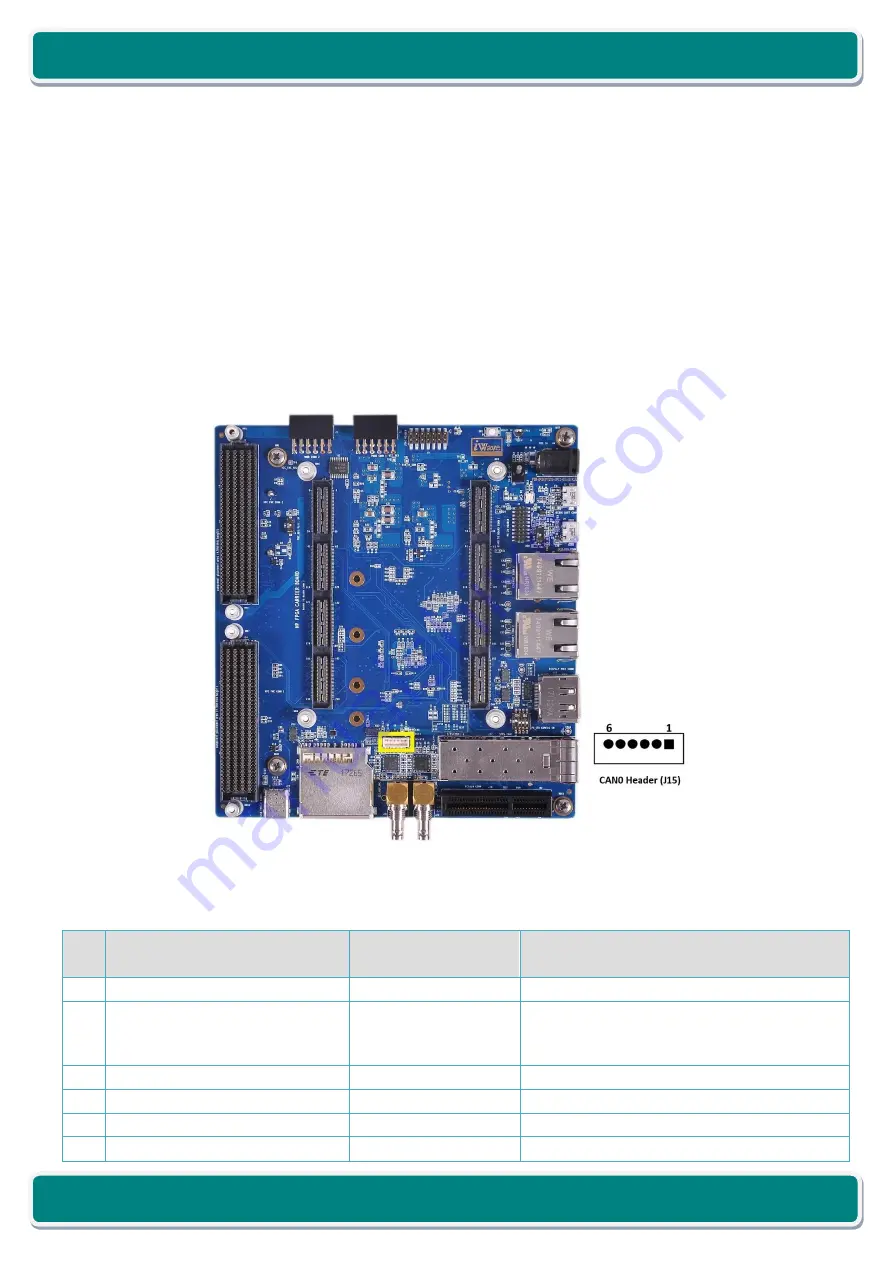

The Zynq Ult MPSoC Carrier board supports one CAN interface through CAN0 interface of Zynq Ult

MPSoC PS. This CAN0 signals are connected from Board to Board connector1 to CAN Bus Transceiver “MCP2562FD”

.

The output of CAN transceiver is connected to 6 pin custom CAN Header (J15). Standby pin of the CAN Bus transceiver

is controlled through PL Bank IO (PL_D12_LVDS46_L9P) from Board to Board Connector1 Pin74. This CAN Header is

physically located at the top of the board as shown below.

Number of Pins

- 6

Connector Part

- 53047-0610 from Molex

Mating Connector

- 0510210600 from Molex with crimping pins

Figure 14: CAN0 Header

Table 8: CAN0 Header Pin Assignment

Pin

No

Pin Name

Signal Type/

Termination

Description

1

VCC_5V

O, 5V Power

5V Supply Voltage.

2

VCC_12V

-

NC.

Note: Optionally connected to on board 12V

through resistor and by default not populated.

3

CANL

IO, DIFF

CAN Differential negative.

4

GND

Power

Ground.

5

CANH

IO, DIFF

CAN Differential positive.

6

GND

Power

Ground.